Les premiers pas

La programmation de l'assembleur 68000 contient des informations détaillées sur les instructions logicielles utilisées par les microprocesseurs et coprocesseurs de la famille M68000, notamment :

| Microprocesseurs | Spécifications |

|---|---|

| MC68000 | Microprocesseur 16/32 bits |

| MC68EC000 | Contrôleur embarqué 16/32 bits |

| MC68HC000 | Microprocesseur basse consommation 16/32 bits |

| MC68008 | Microprocesseur 16 bits avec bus de données 8 bits |

| MC68010 | Microprocesseur à mémoire virtuelle 16/32 bits |

| MC68020 | Microprocesseur à mémoire virtuelle 32 bits |

| MC68EC020 | Contrôleur embarqué 32 bits |

| MC68030 | Microprocesseur amélioré 32 bits de deuxième génération |

| MC68EC030 | Contrôleur embarqué 32 bits |

| MC68040 | Microprocesseur 32 bits de troisième génération |

| MC68LC040 | Microprocesseur 32 bits de troisième génération |

| MC68EC040 | Contrôleur embarqué 32 bits |

| MC68330 | Processeur intégré CPU32 |

| MC68340 | Processeur intégré avec DMA |

| MC68851 | Unité de gestion de mémoire paginée |

| MC68881 | Coprocesseur à virgule flottante |

| MC68882 | Coprocesseur à virgule flottante amélioré |

Remarque

- Toute référence aux MC68000, MC68020 et MC68030 inclut les contrôleurs embarqués correspondants : MC68EC000, MC68EC020 et MC68EC030. Toute référence au MC68040 inclut les MC68LC040 et MC68EC040. Cette convention de référence s'applique à l'ensemble de cette section, sauf indication contraire.

Le modèle de programmation de la famille M68000 comprend deux groupes de registres : utilisateur et superviseur. Les programmes utilisateur exécutés en mode utilisateur utilisent uniquement les registres du groupe utilisateur. Le logiciel système exécuté en mode superviseur a accès à tous les registres et utilise les registres de contrôle du groupe superviseur pour effectuer les fonctions de supervision. Les paragraphes suivants décrivent brièvement les registres des modèles utilisateur et superviseur, ainsi que l'organisation des données dans ces registres.

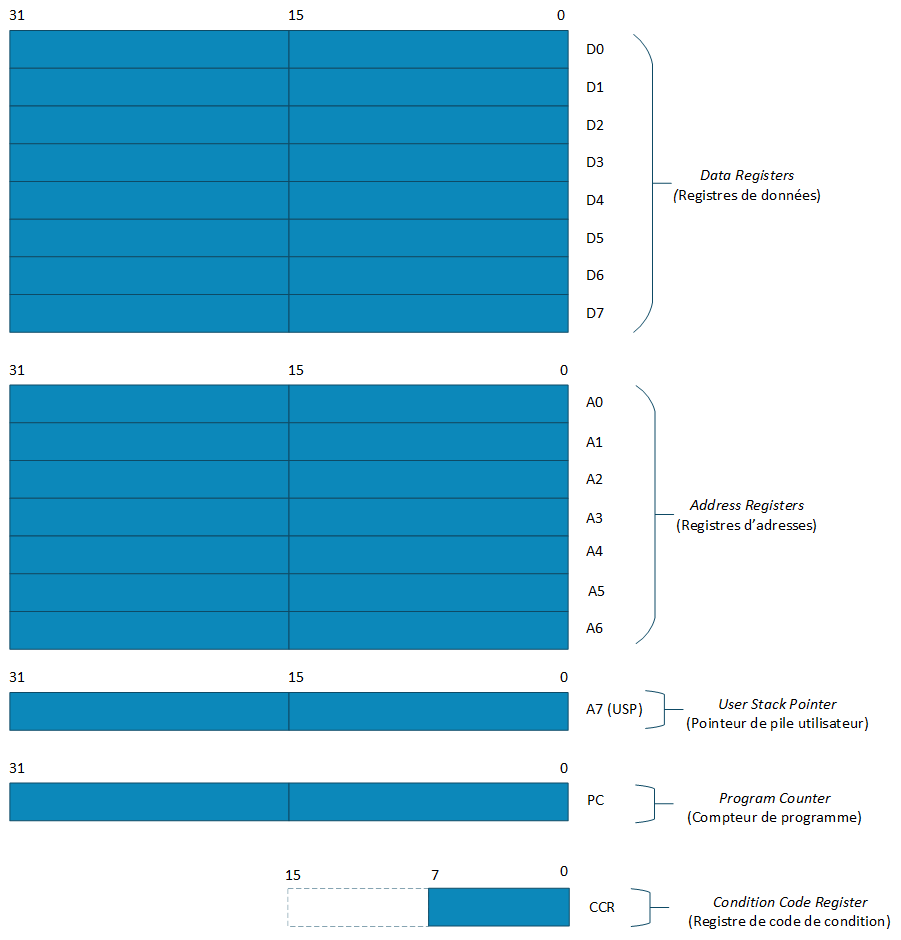

Modèle de programmation utilisateur pour les entiers

La figure suivante illustre la partie entière du modèle de programmation utilisateur. Elle comprend les registres suivants :

- 16 registres généraux 32 bits (D7 à D0, A7 à A0)

- Compteur de programme 32 bits (PC)

- Registre de code de condition 8 bits (CCR)

Registres de données (D7 - D0)

Ces registres servent aux opérations sur les bits et les champs de bits (1 à 32 bits), les octets (8 bits), les mots (16 bits), les mots longs (32 bits) et les quadruples mots (64 bits). Ils peuvent également être utilisés comme registres d'index.

Registres d'adresse (A7 - A0)

Ces registres peuvent servir de pointeurs de pile logiciels, de registres d'index ou de registres d'adresse de base. Ces derniers peuvent être utilisés pour les opérations sur des mots et des mots longs. Le registre A7 est utilisé comme pointeur de pile matériel lors de l'empilement pour les appels de sous-programmes et la gestion des exceptions. Dans le modèle de programmation utilisateur, A7 désigne le pointeur de pile utilisateur (USP).

Compteur de programme

Le compteur de programme (PC) contient l'adresse de l'instruction en cours d'exécution. Lors de l'exécution d'une instruction et du traitement des exceptions, le microprocesseur incrémente automatiquement le PC ou lui attribue une nouvelle valeur. Dans certains modes d'adressage, le PC peut servir de pointeur pour l'adressage relatif.

Registre de code de condition

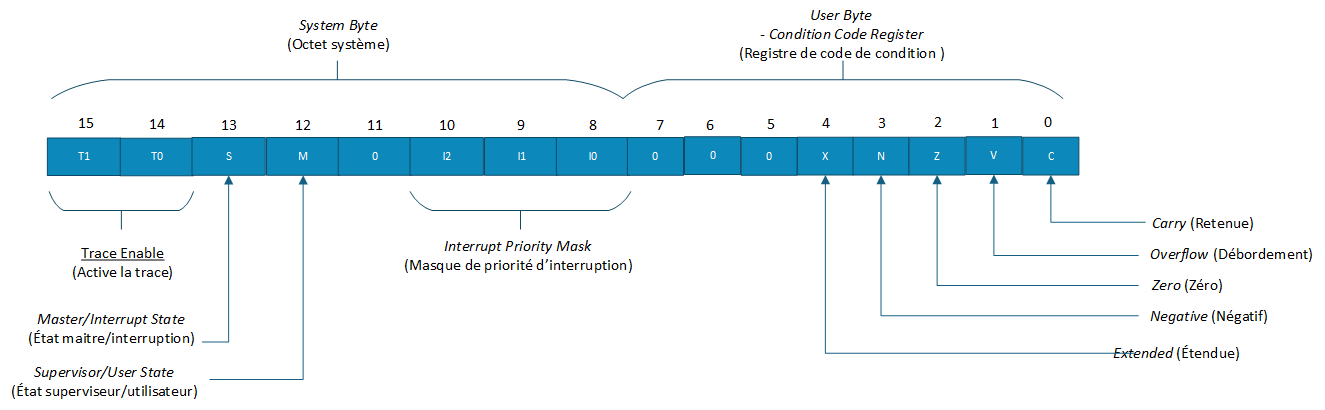

Composé de cinq bits, le CCR, l'octet de poids faible du registre d'état, est la seule partie de ce dernier accessible en mode utilisateur. De nombreuses instructions sur les entiers modifient le CCR, indiquant ainsi leur résultat. Les instructions de contrôle du programme et du système utilisent également certaines combinaisons de ces bits pour gérer le flux d'exécution. Les codes de condition répondent à deux critères : la cohérence entre les instructions, les utilisations et les instances, et des résultats significatifs, sans modification sauf si elle apporte des informations utiles.

La cohérence entre les instructions signifie que toutes les instructions qui sont des cas particuliers d'instructions plus générales modifient les codes de condition de la même manière. La cohérence entre les utilisations signifie que les instructions conditionnelles testent les codes de condition de façon similaire et fournissent les mêmes résultats, qu'une instruction de comparaison, de test ou de déplacement les définisse. La cohérence entre les instances signifie que toutes les instances d'une instruction modifient les codes de condition de la même manière.

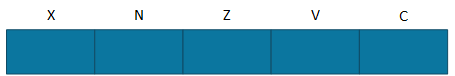

Les quatre premiers bits représentent une condition du résultat généré par une opération. Le cinquième bit, ou bit d'extension (bit X), est un opérande pour les calculs multiprécision. Dans la famille M68000, le bit de retenue (C-bit) et le bit X sont séparés afin de simplifier les techniques de programmation qui les utilisent (voir le tableau 3-18 à titre d'exemple). Dans les définitions du jeu d'instructions, le CCR est illustré comme suit :

- X - Extend : Défini sur la valeur du bit C pour les opérations arithmétiques ; sinon, non affecté ou défini sur un résultat spécifié.

- N - Negative : Insérer si le bit de poids fort du résultat est activé ; sinon, effacer.

- Z - Zero : Insérer si le résultat est égal à zéro ; sinon effacer.

- V - Overflow : Activer si un dépassement de capacité arithmétique se produit, impliquant que le résultat ne peut pas être représenté dans la taille de l'opérande ; sinon, désactiver.

- C - Carry Mettre à 1 si une retenue du bit de poids fort de l'opérande se produit lors d'une addition, ou si un emprunt se produit lors d'une soustraction ; sinon, mettre à 0.

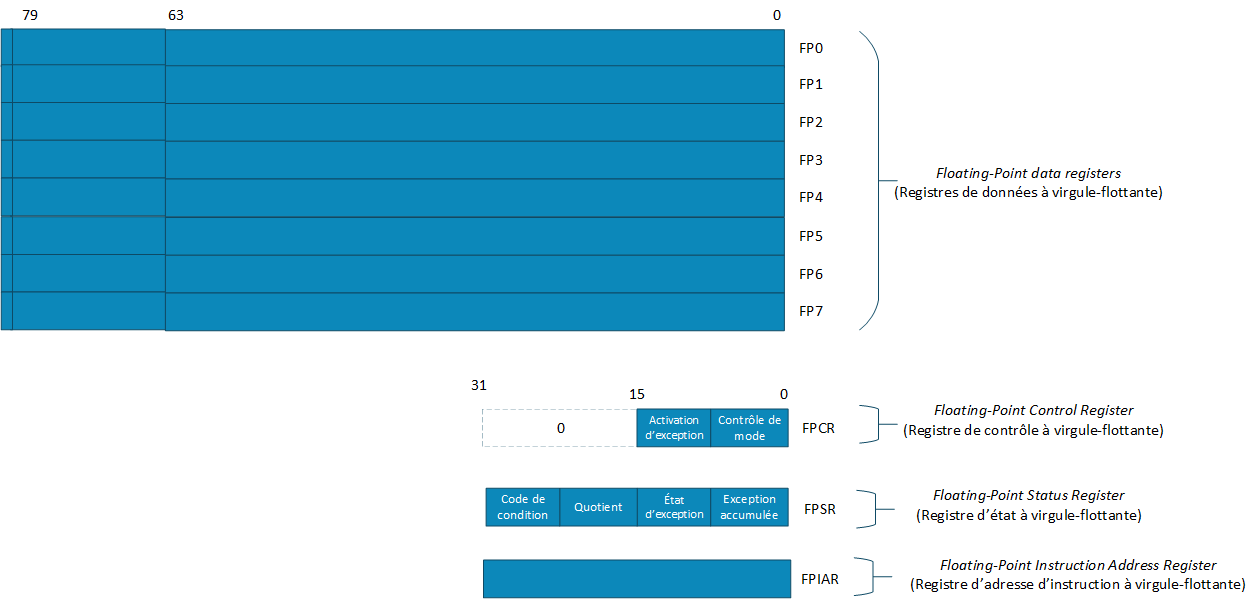

Modèle de programmation utilisateur de l'unité à virgule flottante

Les paragraphes suivants décrivent les registres du modèle de programmation utilisateur de l'unité à virgule flottante. La figure suivante illustre la partie à virgule flottante du modèle de programmation utilisateur de la famille M68000 pour les coprocesseurs à virgule flottante MC68040 et MC68881/MC68882. Ce modèle comprend les registres suivants :

- 8 registres de données à virgule flottante (FP7 - FP0)

- Registre de contrôle à virgule flottante 16 bits (FPCR)

- Registre d'état à virgule flottante 32 bits (FPSR)

- Registre d'adresse d'instruction à virgule flottante 32 bits (FPIAR)

Registres de données à virgule flottante (FP7 - FP0)

Ces registres de données à virgule flottante sont analogues aux registres de données entières de la famille M68000. Ils contiennent toujours des nombres à précision étendue. Tous les opérandes externes, quel que soit leur format, sont convertis en valeurs à précision étendue avant d'être utilisés dans un calcul ou stockés dans un registre de données à virgule flottante. Une opération de réinitialisation ou de restauration à zéro place les registres FP7 à FP0 à la valeur NaN (Not-A-Number) positive et non signalisante.

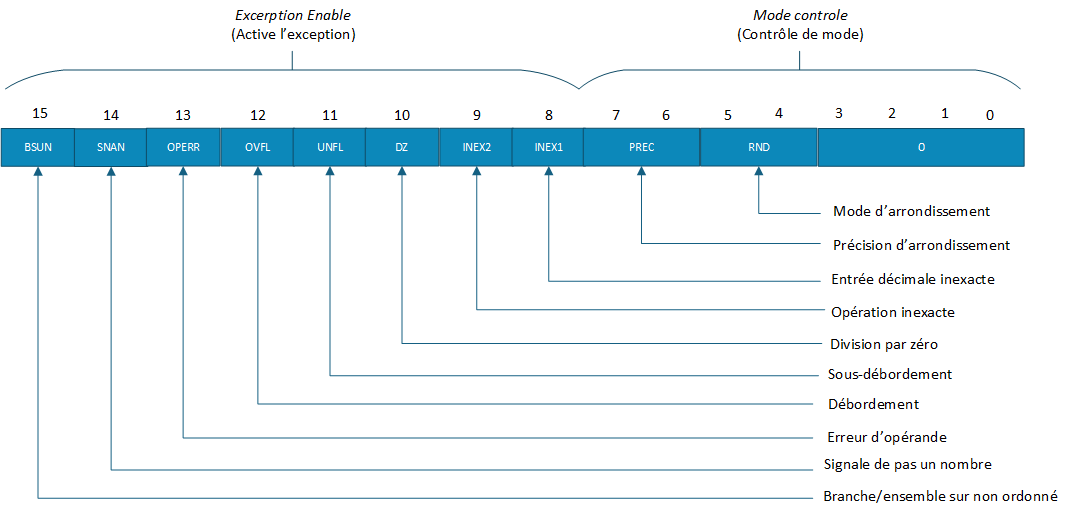

Registre de contrôle des nombres à virgule flottante (FPCR)

Le FPCR (voir la figure suivante) contient un octet d'activation des exceptions (ENABLE) et un octet de contrôle du mode (MODE). L'utilisateur peut lire ou écrire dans le FPCR. Motorola réserve les bits 31 à 16 pour une définition ultérieure ; ces bits sont toujours lus à zéro et sont ignorés lors des opérations d'écriture. La fonction de réinitialisation ou la restauration de l'état nul efface le FPCR. Une fois effacé, ce registre fournit les valeurs par défaut de la norme IEEE 754 pour l'arithmétique binaire à virgule flottante.

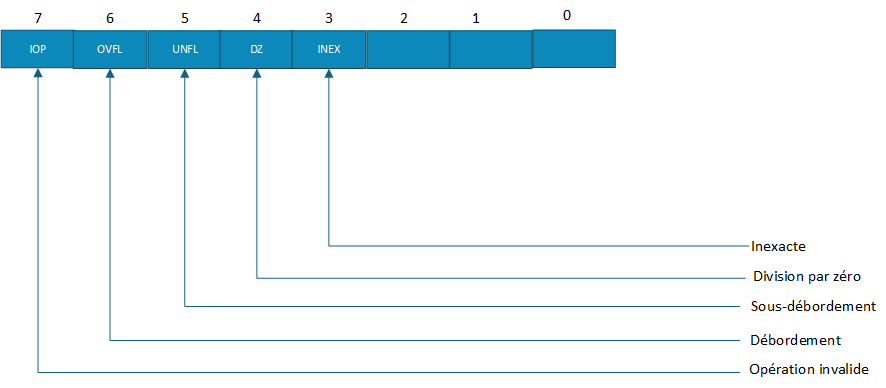

OCTET D'ACTIVATION DES EXCEPTIONS : Chaque bit de l'octet ENABLE (voir la figure suivante) correspond à une classe d'exceptions à virgule flottante. L'utilisateur peut activer séparément les interceptions pour chaque classe d'exceptions à virgule flottante.

OCTET DE CONTRÔLE DU MODE : L'octet MODE (voir figure suivante) contrôle les modes et précisions d'arrondi sélectionnables par l'utilisateur. La valeur zéro dans cet octet sélectionne les valeurs par défaut de la norme IEEE 754. Le champ mode d'arrondi (RND) spécifie comment les résultats inexacts sont arrondis, et le champ précision d'arrondi (PREC) sélectionne la limite d'arrondi de la mantisse. Consultez le suivant pour plus d'informations sur l'encodage.

Registre d'état des nombres à virgule flottante (FPSR)

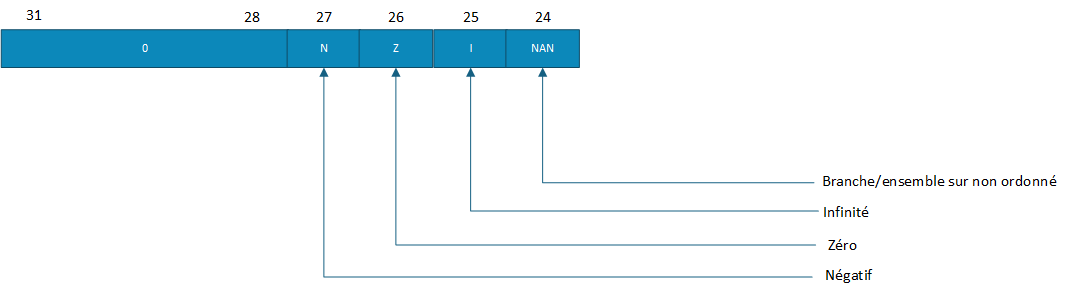

Le FPSR (voir figure précédente) contient un octet de code de condition de nombre à virgule flottante (FPCC), un octet d'état d'exception de nombre à virgule flottante (EXC), un octet de quotient et un octet d'exception accumulée de nombre à virgule flottante (AEXC). L'utilisateur peut lire ou écrire dans tous les bits du FPSR. L'exécution de la plupart des instructions à virgule flottante modifie ce registre. La fonction de réinitialisation ou une opération de restauration de l'état nul efface le FPSR.

Octet de code de condition de nombre à flottante : L'octet FPCC, illustré dans la figure suivante, contient quatre bits de code de condition qui sont positionnés après l'exécution de toutes les instructions arithmétiques impliquant les registres de données à virgule flottante. Les instructions de déplacement d'un registre de données à virgule flottante vers une adresse effective, de déplacement de plusieurs registres de données à virgule flottante et de déplacement d'un registre de contrôle système n'affectent pas le FPCC.

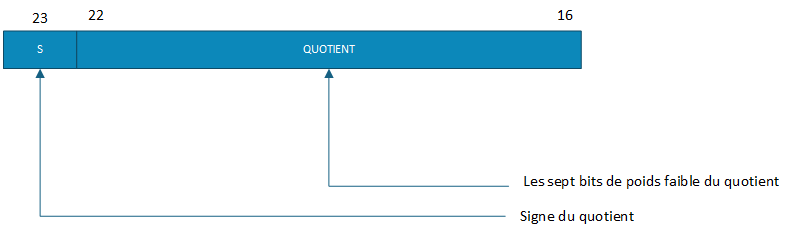

OCTET QUOTIENT : L'octet quotient contient les sept bits de poids faible du quotient non signé ainsi que le signe du quotient entier (voir figure suivante). Les bits quotient peuvent être utilisés pour la réduction d'arguments des fonctions transcendantes et autres. Par exemple, sept bits suffisent amplement pour déterminer le quadrant d'un cercle dans lequel se trouve un opérande. Les bits quotient restent à 1 jusqu'à ce que l'utilisateur les efface.

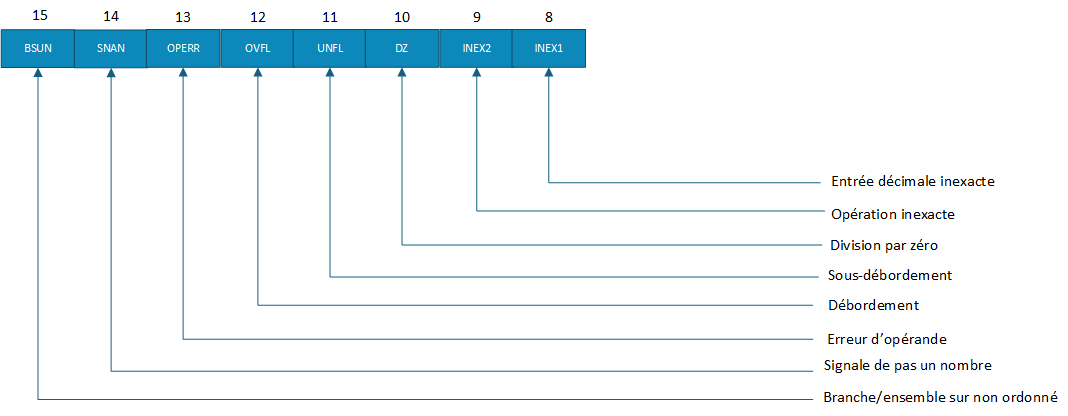

OCTET D'ÉTAT D'EXCEPTION : L'octet EXC, illustré dans la figure suivante, contient un bit pour chaque exception à virgule flottante susceptible de s'être produite lors de la dernière instruction arithmétique ou opération de déplacement. Cet octet est effacé au début de toutes les opérations générant des exceptions à virgule flottante. Les opérations ne générant pas d'exceptions à virgule flottante ne réinitialisent pas cet octet. Un gestionnaire d'exceptions peut utiliser cet octet pour déterminer quelle(s) exception(s) à virgule flottante a/ont provoqué une interruption.

OCTET D'EXCEPTION ACCUMULÉ : L'octet AEXC contient cinq bits d'exception (voir figure suivante) requis par la norme IEEE 754 pour les opérations sans interruption. Ces exceptions sont des combinaisons logiques des bits de l'octet EXC. L'octet AEXC conserve l'historique de toutes les exceptions à virgule flottante survenues depuis sa dernière suppression par l'utilisateur. En fonctionnement normal, seul l'utilisateur peut effacer cet octet en écrivant dans le registre FPSR; toutefois, une réinitialisation ou une restauration de l'état nul peut également l'effacer. De nombreux utilisateurs choisissent de désactiver les interruptions pour tout ou partie des classes d'exceptions à virgule flottante. L'octet AEXC évite d'interroger l'octet EXC après chaque instruction à virgule flottante. À la fin de la plupart des opérations (FMOVEM et FMOVE exclues), les bits de l'octet EXC sont combinés logiquement pour former une valeur AEXC, qui est ensuite combinée par un OU logique avec l'octet AEXC existant. Cette opération crée des bits d'exception à virgule flottante « collants » dans l'octet AEXC que l'utilisateur n'a besoin d'interroger qu'une seule fois, c'est-à-dire à la fin d'une série d'opérations à virgule flottante :

L'activation ou la désactivation des bits AEXC ne provoque ni n'empêche une exception. Les équations suivantes illustrent la relation entre l'octet EXC et l'octet AEXC. La comparaison de la valeur actuelle du bit AEXC avec une combinaison de bits de l'octet EXC permet de calculer une nouvelle valeur pour le bit AEXC correspondant. Ces équations s'appliquent à la configuration des bits AEXC à la fin de chaque opération affectant l'octet AEXC :

| Nouveau bit AEXC | = Ancien bit AEXC | V | Bits EXC |

|---|---|---|---|

| IOP | = IOP | V | (SNAN V OPERR) |

| OVFL | = OVFL | V | (OVFL) |

| UNFL | = UNFL | V | (UNFL L INEX2) |

| DZ | = DZ | V | (DZ) |

| INEX | = INEX | V | (INEX1 V INEX2 V OVFL) |

Registre d'adresse des instructions à virgule flottante (FPIAR)

L'unité de calcul entier peut exécuter des instructions pendant que l'unité de calcul à virgule flottante (FPU) exécute simultanément une instruction à virgule flottante. De plus, la FPU peut exécuter simultanément deux instructions à virgule flottante. En raison de cette exécution non séquentielle des instructions, la valeur du compteur ordinal (PC) empilée par la FPU, en réponse à une interruption d'exception à virgule flottante, peut ne pas pointer vers l'instruction fautive.

Pour les instructions de la FPU générant des interruptions d'exception, le registre FPIAR 32 bits est initialisé avec l'adresse logique de l'instruction avant son exécution par le processeur. Le gestionnaire d'exceptions à virgule flottante peut utiliser cette adresse pour localiser l'instruction à virgule flottante ayant provoqué l'exception. Étant donné que les instructions FMOVE de la FPU vers/depuis le registre FPCR, le registre FPSR ou le registre FPIAR, ainsi que les instructions FMOVEM, ne peuvent pas générer d'exceptions à virgule flottante, elles ne modifient pas le registre FPIAR. Une réinitialisation ou une restauration à zéro efface le registre FPIAR.

Modèle de programmation superviseur

Les programmeurs système utilisent le modèle de programmation superviseur pour implémenter les fonctions sensibles du système d'exploitation, telles que les sous-systèmes de contrôle des entrées/sorties et de gestion de la mémoire (MMU). Les paragraphes suivants décrivent brièvement les registres du modèle de programmation superviseur. Leur accès est réservé aux instructions privilégiées. Le tableau suivant répertorie les registres superviseur et les processeurs non liés à la gestion de la mémoire paginée. Pour plus d'informations sur la programmation de la gestion de la mémoire paginée, veuillez consulter le manuel utilisateur spécifique au périphérique. Le tableau suivant répertorie les registres superviseur et les processeurs liés à la gestion de la mémoire paginée :

| Registres | Périphériques | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 68000 68008 68HC000 68HC001 68EC000 |

68010 | 68020 68EC020 |

CPU32 | 68030 | 68EC030 | 68040 | 68EC040 | 68LC040 | |

| AC1, AC0 | X | ||||||||

| ACUSR | X | ||||||||

| CAAR | x | x | x | ||||||

| CACR | x | x | x | x | x | x | |||

| DACR1, DACR0 | x | ||||||||

| DFC | x | x | x | x | x | x | x | x | |

| DTT1, DTT0 | x | x | |||||||

| IACR1, IACR0 | x | ||||||||

| ITT1, ITT0 | x | x | |||||||

| MSP | x | x | x | x | x | x | |||

| SFC | x | x | x | x | x | x | x | x | |

| SR | x | x | x | x | x | x | x | x | x |

| SSP/ISP | x | x | x | x | x | x | x | x | x |

| TT1, TT0 | x | ||||||||

| VBR | x | x | x | x | x | x | x | x | |

| Abréviation | Nom | Description | |||||

|---|---|---|---|---|---|---|---|

| AC1, AC0 | Access Control Registers | Registres de contrôle d'accès | |||||

| ACUSR | Access Control Unit Status Register | Registre d'état de l'unité de contrôle d'accès | |||||

| CAAR | Cache Address Register | Registre d'adresses du cache | |||||

| CACR | Cache Control Register | Registre de contrôle du cache | |||||

| DACR1, DACR0 | Data Access ControlRegisters | Registres de contrôle d'accès aux données | |||||

| DFC | Destination Function Code Register | Registre des codes de fonction de destination | |||||

| DTT1, DTT0 | Data Transparent Translation Registers | Registres de traduction transparents pour les données | |||||

| IACR1, IACR0 | Instruction Access Control Registers | Registres de contrôle d'accès aux instructions | |||||

| ITT1, ITT0 | Instruction Transparent Translation Registers | Registres de traduction transparents des instructions | |||||

| MSP | Master Stack Pointer Register | Registre pointeur de pile principal | |||||

| SFC | Source Function Code Register | Registre du code de fonction source | |||||

| SR | Status Register | Registre d'état | |||||

| SSP/ISP | Supervisor and Interrupt Stack Pointer | Superviseur et pointeur de pile d'interruption | |||||

| TT1, TT0 | Transparent Translation Registers | Registres de traduction transparents | |||||

| VBR | Vector Base Register | Registre de base vectoriel | |||||

| Registres | Périphériques | |||

|---|---|---|---|---|

| 68851 | 68030 | 68040 | 68LC040 | |

| AC | x | |||

| CAL | x | |||

| CRP | x | x | ||

| DRP | x | |||

| PCSR | x | |||

| PMMUSR, MMUSR | x | x | x | x |

| SCC | x | |||

| SRP | x | x | x | x |

| TC | x | x | x | x |

| URP | x | x | ||

| VAL | x | |||

| Abréviation | Nom | Description |

|---|---|---|

| AC | Access Control Register | Registre de contrôle d'accès |

| CAL | Current Access Level Register | Registre des niveaux d'accès actuels |

| CRP | CPU Root Pointer | Pointeur racine du microprocesseur |

| DRP | DMA Root Pointer | Pointeur racine DMA |

| PCSR | PMMU Control Register | Registre de contrôle PMMU |

| PMMUSR | Paged Memory Management Unit Status Register | Registre d'état de l'unité de gestion de mémoire paginée |

| MMUSR | Memory Management Unit Status Register | Registre d'état de l'unité de gestion de la mémoire |

| SCC | Stack Change Control Register | Registre de contrôle des modifications de pile |

| SRP | Supervisor Root Pointer Register | Registre de pointeur racine du superviseur |

| TC | Translation Control Register | Registre de contrôle des traductions |

| URP | User Root Pointer | Pointeur racine utilisateur |

| VAL | Valid Access Level Register | Registre des niveaux d'accès valides |

Registre d'adresse 7 (A7)

Dans le modèle de programmation superviseur, le registre A7 désigne le pointeur de pile d'interruption, A7' (ISP), et le pointeur de pile maître, A7" (MSP). Le pointeur de pile superviseur est le pointeur de pile actif (ISP ou MSP). Pour les processeurs ne prenant pas en charge ISP ou MSP, la pile système est désignée par le pointeur de pile système (SSP). ISP et MSP sont des registres d'adresse à usage général pour le mode superviseur. Ils peuvent être utilisés comme pointeurs de pile logiciels, registres d'index ou registres d'adresse de base. ISP et MSP peuvent être utilisés pour des opérations sur des mots et des mots longs.

Registre d'état

La figure suivante illustre le registre d'état (SR), entreposant l'état du microprocesseur et contient les codes de condition reflétant les résultats d'une opération précédente. En mode superviseur, le logiciel peut accéder à l'intégralité du SR, y compris le masque de priorité d'interruption et les bits de contrôle supplémentaires. Ces bits indiquent les états suivants du processeur : l'un des deux modes de traçage (T1, T0), le mode superviseur ou utilisateur (S) et le mode maître ou d'interruption (M). Pour les MC68000, MC68EC000, MC68008, MC68010, MC68HC000, MC68HC001 et CPU32, un seul mode de traçage est pris en charge (T0 est toujours à zéro) et une seule pile système (le bit M est toujours à zéro). Les bits I2, I1 et I0 définissent le niveau du masque d'interruption :

| T1 | T0 | Mode de trace |

|---|---|---|

| 0 | 0 | Pas de trace |

| 1 | 0 | Suivre toute instruction |

| 0 | 1 | Trace sur le changement de débit |

| 1 | 1 | Indéfini |

| S | M | Pile active |

|---|---|---|

| 0 | x | USP |

| 1 | 0 | ISP |

| 1 | 1 | MSP |

Registre de base des vecteurs (VBR)

Le VBR contient l'adresse de base de la table des vecteurs d'exception en mémoire. Le déplacement d'un vecteur d'exception incrémente la valeur de ce registre, qui accède à la table des vecteurs.

Registres de codes de fonction alternatifs (SFC et DFC)

Les registres de codes de fonction alternatifs contiennent des codes de fonction de 3 bits. Ces codes peuvent être considérés comme des extensions de l'adresse logique 32 bits, qui peut fournir jusqu'à huit espaces d'adressage de 4 Go. Le processeur génère automatiquement les codes de fonction pour sélectionner les espaces d'adressage des données et des programmes en modes utilisateur et superviseur. Certaines instructions utilisent les registres SFC et DFC pour spécifier les codes de fonction des opérations.

Registre d'état de l'unité de contrôle d'accès (MC68EC030 uniquement)

Le registre d'état de l'unité de contrôle d'accès (ACUSR) est un registre 16 bits contenant les informations d'état renvoyées par l'exécution de l'instruction PTEST. Cette instruction recherche dans les registres de contrôle d'accès (AC) une correspondance avec une adresse spécifiée. Une correspondance dans l'un ou l'autre des registres AC active le bit 6 de l'ACUSR. Tous les autres bits de l'ACUSR sont indéfinis et ne doivent pas être utilisés.

Registres de traduction transparente/de contrôle d'accès

L'expression «traduction transparente» est en réalité impropre, car l'espace d'adressage entier est traduit de manière transparente aussi bien dans un environnement de contrôle embarqué sans unité de gestion de la mémoire (MMU) intégrée que dans les processeurs dotés d'une MMU. Pour les processeurs avec MMU intégrée, tels que les MC68030, MC68040 et MC68LC040, les registres de traduction transparente (TT) définissent des blocs d'adresses logiques étant traduits de manière transparente en adresses physiques correspondantes. Ces registres sont indépendants de la MMU intégrée. Pour les contrôleurs embarqués, tels que les MC68EC030 et MC68EC040, les registres de contrôle d'accès (AC) ont une fonction similaire aux registres TT, mais portent un nom différent. La fonction principale des registres AC est de définir des blocs d'espace d'adressage qui contrôlent des propriétés de cet espace, comme la mise en cache. Les paragraphes suivants décrivent ces registres.

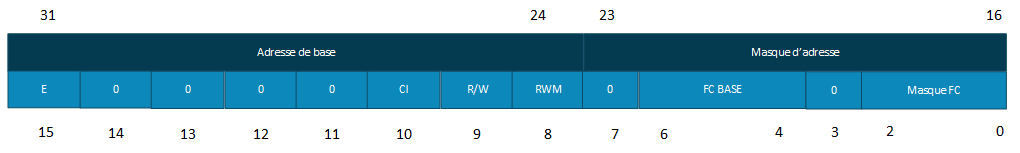

CHAMPS DE REGISTRE DE TRADUCTION TRANSPARENTE/CONTRÔLE D'ACCÈS POUR LE M68030 : La figure suivante illustre le format du registre de traduction transparente MC68030/contrôle d'accès MC68EC030 :

| Nom | Description |

|---|---|

| Adresse de base | Ce champ de 8 bits est comparé aux bits d'adresse A31 à A24. Les adresses qui correspondent à cette comparaison (et étant par ailleurs éligibles) sont traduites de manière transparente/contrôlées en accès. |

| Masque d'adresse | Ce champ de 8 bits contient un masque pour le champ de base de l'adresse. Activer un bit dans ce champ entraîne l'ignorance du bit correspondant du champ de base de l'adresse. Les blocs de mémoire supérieurs à 16 Mo peuvent être gérés de manière transparente en configurant certains bits logiques du masque d'adresse à 1. Les bits de poids faible de ce champ sont généralement activés pour définir des blocs contigus supérieurs à 16 Mo, mais cela n'est pas obligatoire. |

| E - Activer | 0 = Traduction transparente/contrôle d'accès désactivé 1 = Traduction transparente/contrôle d'accès activé |

| CI - Inhibition du cache | 0 = Mise en cache autorisée 1 = Mise en cache inhibée |

| R/W - Lecture/Écriture | 0 = Accès en écriture uniquement 1 = Accès en lecture uniquement |

| Masque de lecture/écriture (R/WM) | 0 = Champ R/W utilisé 1 = Champ R/W ignoré |

| FC BASE - Code de fonction de base | Ce champ de 3 bits définit le code de fonction de base pour les accès étant traduits de manière transparente avec ce registre. Les adresses dont le code de fonction correspond au champ FC BASE (et étant par ailleurs éligibles) sont traduites de manière transparente. |

| Masque de code de fonction (FC MASK) | Ce champ de 3 bits contient un masque pour le champ FC BASE. L'activation d'un bit dans ce champ entraîne l'ignorance du bit correspondant du champ FC BASE. |

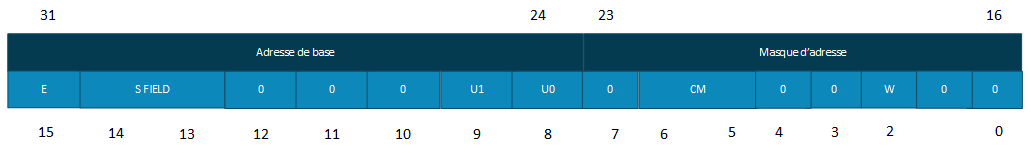

CHAMPS DE REGISTRE DE TRADUCTION TRANSPARENTE/CONTRÔLE D'ACCÈS POUR LE M68040 : La figure suivante illustre le format du registre de traduction transparente MC68040 et MC68LC040/MC68EC040 :

| Nom | Description |

|---|---|

| Adresse de base | Ce champ de 8 bits est comparé aux bits d'adresse A31 à A24. Les adresses correspondant à cette comparaison (et étant par ailleurs éligibles) sont traduites de manière transparente/contrôlées en accès. |

| Masque d'adresse | Ce champ de 8 bits contient un masque pour le champ de base de l'adresse. Activer un bit dans ce champ entraîne l'ignorance du bit correspondant dans le champ de base de l'adresse. Les blocs de mémoire supérieurs à 16 Mo peuvent être traduits de manière transparente (contrôlés en accès) en activant certains bits logiques du masque d'adresse. Les bits de poids faible de ce champ sont généralement activés pour définir des blocs contigus supérieurs à 16 Mo, mais cela n'est pas obligatoire. |

| E - Activer | Ce bit active ou désactive la traduction transparente/le contrôle d'accès du bloc défini par ce registre : 0 = Traduction transparente/contrôle d'accès désactivé 1 = Traduction transparente/contrôle d'accès activé |

| S - Mode superviseur/utilisateur | Ce champ spécifie l'utilisation du FC2 pour la correspondance d'une adresse : 00 = Correspondance uniquement si FC2 vaut 0 (accès en mode utilisateur) 01 = Correspondance uniquement si FC2 vaut 1 (accès en mode superviseur) 1X = Ignorer le FC2 lors de la correspondance |

| U1, U2 - Attributs de la page utilisateur | Les MC68040, MC68E040 et MC68LC040 n'interprètent pas ces bits définis par l'utilisateur. Si l'accès entraîne un transfert sur le bus externe, les valeurs U0 et U1 sont respectivement renvoyées aux signaux UPA0 et UPA1. |

| CM - Mode de cache | Ce champ permet de sélectionner le mode de cache et la sérialisation d'accès d'une page : 00 = Mise en cache, écriture immédiate 01 = Mise en cache, copie différée 10 = Non mise en cache, sérialisée 11 = Non mise en cache |

| W - Protection en écriture | Ce bit indique si le bloc est protégé en écriture. S'il est activé, les accès en écriture et en lecture-modification-écriture sont annulés comme si le bit de résidence dans un descripteur de table était désactivé : 0 = Accès en lecture et en écriture autorisés 1 = Accès en écriture interdits |

Formats de données entières

Les formats de données des opérandes pris en charge par l'unité entière, répertoriés dans le tableau suivant, incluent ceux pris en charge par le MC68030, ainsi qu'un nouveau format de données (bloc de 16 octets) pour l'instruction MOVE16. Les opérandes de l'unité entière peuvent résider dans des registres, en mémoire ou dans les instructions elles-mêmes. La taille des opérandes pour chaque instruction est soit explicitement codée dans l'instruction, soit implicitement définie par l'opération de l'instruction :

| Format des données des opérandes | Taille | Notes |

|---|---|---|

| Bit | 1 bit | - |

| Champ de bits | Bits 1 à 32 | Champ de bits consécutifs |

| Décimal codé binaire (BCD) | 8 bits | Compressé : 2 chiffres/octet ; Décompressé : 1 chiffre/octet |

| Octet Entier | 8 bits | - |

| Entier (mot) | 16 bits | - |

| Entier long (mot long) | 32 bits | - |

| Entier quadruple mot | 64 bits | Deux registres de données quelconques |

| 16 octets | 128 bits | Mémoire uniquement, alignée sur une limite de 16 octets |

Formats de données à virgule flottante

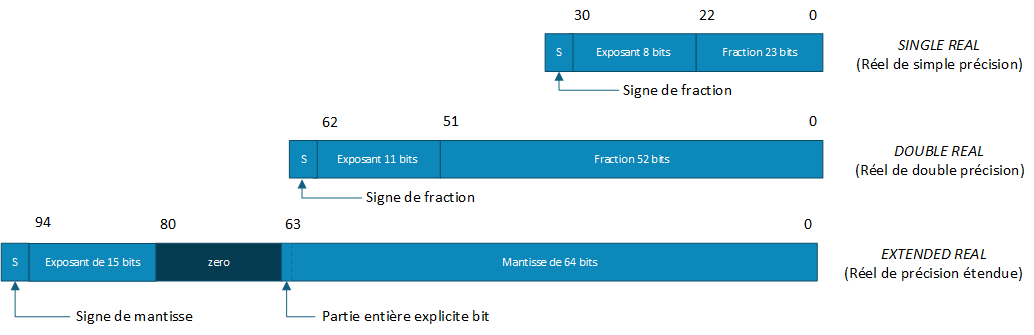

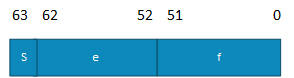

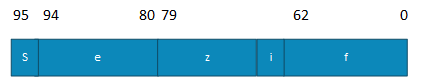

Les paragraphes suivants décrivent les formats de données des opérandes de l'unité de calcul en virgule flottante (FPU). La FPU prend en charge sept formats de données. Il existe trois formats d'entiers binaires signés (octet, mot et mot long) identiques à ceux pris en charge par l'unité d'entiers. La FPU prend en charge le format décimal réel compacté. Les MC68881 et MC68882 prennent en charge ce format matériellement, et les processeurs à partir du MC68040 le prennent en charge logiciellement. La FPU prend également en charge trois formats binaires à virgule flottante (simple, double et précision étendue) entièrement conformes à la norme IEEE 754. Toute référence au format de précision étendue dans cette section désigne le format de double précision étendue défini par la norme IEEE 754.

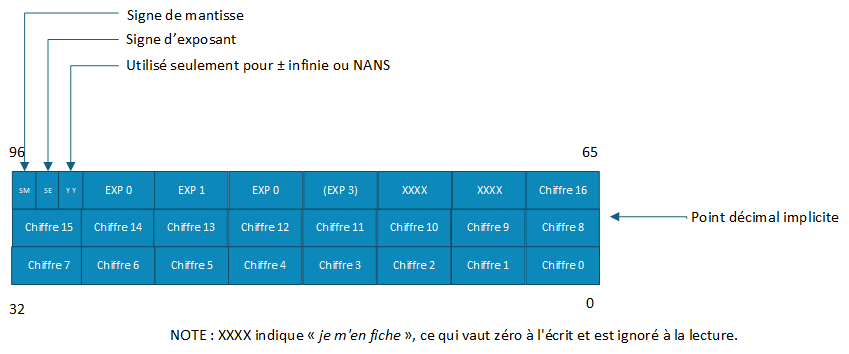

Format réel décimal compacté

La figure suivante illustre le format réel décimal compacté, composé de trois mots longs : un exposant de 3 chiffres en base 10 et une mantisse de 17 chiffres en base 10. Les deux premiers mots longs, chiffres 15 à 0, sont codés sur 64 bits et correspondent directement aux positions 63 à 0 du format réel à précision étendue. Deux bits de signe distincts sont utilisés : un pour l'exposant et l'autre pour la mantisse. Un exposant supplémentaire (EXP3) est défini pour gérer les dépassements de capacité pouvant survenir lors de la conversion du format réel à précision étendue vers le format réel décimal compacté :

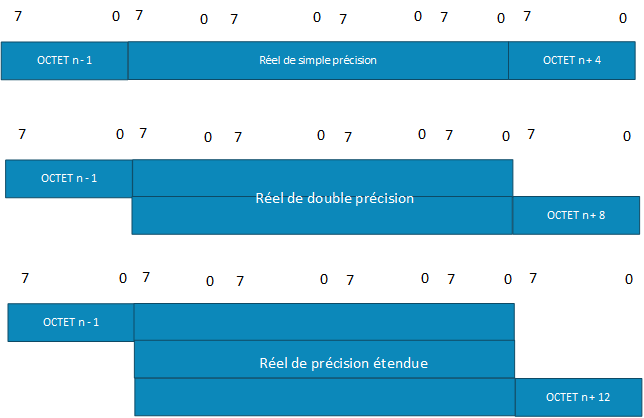

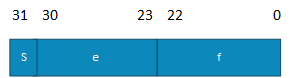

Formats binaires à virgule flottante

La figure suivante illustre les trois formats de données binaires à virgule flottante. L'exposant, dans ces trois formats, est un entier binaire non signé auquel est ajouté un biais implicite. La soustraction de ce biais à la valeur de l'exposant donne une puissance de deux en complément à deux signé. Ce résultat, multiplié par la mantisse, correspond à la magnitude d'un nombre à virgule flottante normalisé. Un programme peut exécuter une instruction CMP comparant des nombres à virgule flottante en mémoire en utilisant des exposants biaisés, indépendamment de la magnitude absolue de ces exposants.

Les formats de données pour les nombres en simple et double précision diffèrent légèrement de ceux des nombres en précision étendue dans la représentation de la mantisse. Pour les trois précisions, une mantisse normalisée est toujours comprise entre 1 et 2. Le format de données en précision étendue représente la mantisse entière, y compris le bit de la partie entière. Les formats de données en simple et double précision ne représentent qu'une portion fractionnaire de la mantisse (la partie entière) et impliquent toujours que la partie entière vaut 1.

La norme IEEE 754 a introduit le terme «mantisse» pour faire la distinction entre «mantisse» et «fraction» et éviter les connotations historiques du terme «mantisse». La norme IEEE 754 définit la mantisse comme la composante d'un nombre binaire à virgule flottante comprenant un bit de poids fort, explicite ou implicite, à gauche de la virgule. Toutefois, ce manuel utilise le terme «mantisse» pour les formats à précision étendue et le terme «fraction» pour les formats à simple et double précision, au lieu du terme « mantisse » de la norme IEEE.

Remarque : Cette section définit les intervalles à l'aide de la notation ensembliste traditionnelle, avec le format « borne...borne » indiquant les limites de l'intervalle. Le type de crochets encadrant l'intervalle précise si la borne est incluse ou exclue. Un crochet indique l'inclusion, et une parenthèse indique l'exclusion. Par exemple, l'intervalle « [1,0...2,0] » définit l'intervalle des nombres supérieurs ou égaux à 1,0 et inférieurs ou égaux à 2,0. L'intervalle « (0,0...+∞) » définit l'intervalle des nombres supérieurs à 0,0 et inférieurs à l'infini positif, mais différents de 0,0.

Types de données à virgule flottante

Chaque format de données à virgule flottante prend en charge cinq types de données uniques : 1) les nombres normalisés, 2) les nombres dénormalisés, 3) les zéros, 4) les infinis et 5) les NaN. Les valeurs d'exposant dans chaque format représentent ces types de données spéciaux. Le type de données normalisé n'utilise jamais la valeur d'exposant maximale ou minimale pour un format donné, sauf pour le format à précision étendue. Le format de données réelles décimales compactées ne prend pas en charge les nombres dénormalisés.

Il existe une différence subtile entre la définition d'un nombre à précision étendue avec un exposant égal à zéro et celle d'un nombre à précision simple ou double avec un exposant égal à zéro. L'exposant nul d'un nombre à précision simple ou double dénormalise la définition du nombre, et le bit entier implicite est nul. Un nombre à précision étendue avec un exposant nul peut avoir un bit entier explicite égal à un. Cela donne un nombre normalisé, bien que l'exposant soit égal à la valeur minimale. Par souci de simplicité, la discussion qui suit traite les trois formats à virgule flottante de la même manière : un exposant nul indique un nombre dénormalisé. Toutefois, il convient de noter que le format à précision étendue peut déroger à cette règle.

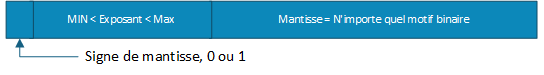

Nombres normalisés

Les nombres normalisés comprennent tous les nombres dont l'exposant est compris entre les valeurs maximale et minimale. Ils peuvent être positifs ou négatifs. En simple et double précision, le bit entier implicite vaut 1. En précision étendue, le bit de poids fort de la mantisse (bit entier explicite) ne peut être que 1 (voir figure suivante) ; l'exposant peut être nul :

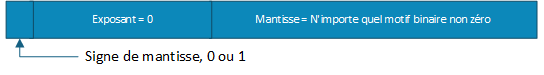

Nombres dénormalisés

Les nombres dénormalisés représentent des valeurs réelles proches du seuil de dépassement de capacité négatif. Le dépassement de capacité négatif est détecté pour un format de données et une opération donnés lorsque l'exposant du résultat est inférieur ou égal à la valeur minimale de l'exposant. Les nombres dénormalisés peuvent être positifs ou négatifs. En simple et double précision, le bit entier implicite est à zéro. En précision étendue, le bit de poids fort (MSB) de la mantisse, représentant l'entier explicite, ne peut être que nul (voir figure suivante) :

Traditionnellement, la détection d'un dépassement de capacité négatif (ou sous-dépassement) entraîne une mise à zéro des systèmes de nombres à virgule flottante. Ceci crée un grand écart sur la droite numérique entre le nombre normalisé de plus petite magnitude et zéro. La norme IEEE 754 implémente des sous-dépassements progressifs : la mantisse du résultat est décalée vers la droite (dénormalisation) tandis que son exposant est incrémenté jusqu'à atteindre sa valeur minimale. Si tous les bits de la mantisse sont décalés vers la droite lors de cette dénormalisation, le résultat devient nul. Généralement, un sous-dépassement progressif limite les dommages potentiels à une simple erreur d'arrondi. Cette description du sous-dépassement et de la dénormalisation ne tient pas compte des effets de l'arrondi ni des modes d'arrondi sélectionnables par l'utilisateur. Ainsi, le grand écart sur la droite numérique créé par les systèmes de nombres à zéro est comblé par des nombres représentables (dénormalisés) dans le système de nombres à virgule flottante à sous-dépassement progressif de la norme IEEE.

Le format de données à précision étendue comportant un bit entier explicite, un nombre peut être formaté avec un exposant non nul, inférieur à la valeur maximale, et un bit entier nul. La norme IEEE 754 ne définit pas de bit entier nul. Un tel nombre est un nombre non normalisé. Le matériel ne prend pas directement en charge les nombres dénormalisés et non normalisés, mais les prend en charge implicitement en les interceptant comme des types de données non implémentés, ce qui permet une conversion efficace par logiciel.

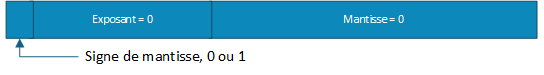

Zéros

Les zéros peuvent être positifs ou négatifs et représentent les valeurs réelles + 0,0 et - 0,0 (voir figure suivante) :

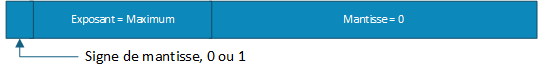

Infinis

Les infinis peuvent être positifs ou négatifs et représentent des valeurs réelles dépassant le seuil de dépassement. Un exposant supérieur ou égal à la valeur maximale de l'exposant indique un dépassement pour un format de données et une opération donnés. Cette description du dépassement ne tient pas compte des effets d'arrondi ni des modèles d'arrondi sélectionnables par l'utilisateur. Pour les infinis en simple et double précision, la fraction est nulle. Pour les infinis en précision étendue, le bit de poids fort (MSB) de la mantisse, c'est-à-dire le bit entier explicite, peut être égal à 1 ou à 0 (voir figure suivante) :

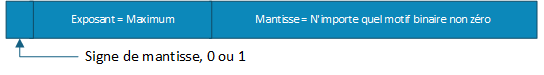

Valeurs NaN (Not-A-Numbers)

Lorsqu'elles sont créées par l'unité de calcul en virgule flottante (FPU), les valeurs NaN représentent les résultats d'opérations sans interprétation mathématique, comme la division de l'infini par l'infini. Toute opération prenant une valeur NaN en entrée renvoie un résultat NaN. Lorsqu'elles sont créées par l'utilisateur, les valeurs NaN peuvent protéger contre les variables et les tableaux non initialisés ou représenter des types de données définis par l'utilisateur. Pour les valeurs NaN à précision étendue, le bit de poids fort (MSB) de la mantisse, le bit entier explicite, peut être égal à 1 ou à 0 (voir figure suivante) :

L'unité de calcul en virgule flottante (FPU) implémente deux types de valeurs NaN, identifiées par la valeur du bit de poids fort (MSB) de la mantisse pour la simple et la double précision, et par le MSB de la mantisse moins un pour la précision étendue. Si le bit est à 1, il s'agit d'une valeur NaN non signalante; sinon, il s'agit d'une valeur NaN non signalante (SNAN). Une SNAN peut servir de mécanisme d'échappement pour un type de données non IEEE défini par l'utilisateur. La FPU ne crée jamais de SNAN à la suite d'une opération.

La spécification IEEE définit le traitement des valeurs NaN utilisées comme entrée d'une opération. Une valeur NaN non signalante doit être renvoyée lorsqu'une SNAN est utilisée comme entrée et qu'une interruption SNAN est désactivée. La FPU effectue cette opération en utilisant la SNAN source, en positionnant le MSB de la mantisse et en stockant la valeur NaN non signalante résultante dans la destination. En raison des formats IEEE pour les valeurs NaN, la mise à 1 du MSB d'une SNAN produit toujours une valeur NaN non signalante.

Lorsqu'une unité de calcul en virgule flottante (FPU) crée une valeur NaN, celle-ci contient toujours la même séquence de bits dans sa mantisse. Tous les bits de la mantisse sont à 1, quelle que soit la précision. Lorsqu'un utilisateur crée une valeur NaN, n'importe quelle séquence de bits non nulle peut être entreposée dans la mantisse.

Résumé des formats et types de données

Les tableaux précédent récapitulent les spécifications des types de données pour les formats de données à simple, double et grande précision. Les formats décimaux réels compactés prennent en charge tous les types de données, à l'exception des nombres dénormalisés. Le tableau suivant récapitule les types de données pour le format décimal réel compacté:

Format de données récapitulatives en format réel simple précision :

| Taille du champ en bits | |

|---|---|

| Signe(s) | 1 |

| Exposant biaisé (e) | 8 |

| Fraction (f) | 23 |

| Total | 32 |

| Interprétation du signe | |

|---|---|

| Fraction positive | s = 0 |

| Fraction négative | s = 1 |

| Nombres normalisés | |

|---|---|

| Biais de l'exposant biaisé | +127 ($7F) |

| Intervalle d'exposants biaisés | 0 < e < 255 ($FF) |

| Intervalle de valeurs de la fraction | Zéro ou non nul |

| Fraction | 1.f |

| Relation avec la représentation des nombres réels | (-1)s × 2e-127 × 1. |

| Nombres dénormalisés | |

|---|---|

| Format d'exposant biaisé minimum | 0 ($00) |

| Biais de l'exposant biaisé | +126 ($7E) |

| Intervalle de valeurs de la fraction | Non nulle |

| Fraction | 0.f |

| Relation avec la représentation des nombres réels | (-1)s × 2-126 × 0.f |

| Zéros signés | |

|---|---|

| Format d'exposant biaisé minimum | 0 ($00) |

| Fraction | 0.f = 0.0 |

| Infinis signés | |

|---|---|

| Format d'exposant biaisé maximum | 255 ($FF) |

| Fraction | 0.f = 0.0 |

| NAN | |

|---|---|

| Signe | Indifférent («Je m'en fiche») |

| Format d'exposant biaisé maximum | 255 ($FF) |

| Fraction | Non zéro |

| Représentation d'une fraction Sans signalisation Avec signalisation Motif binaire non nul créé par l'utilisateur Fraction générée par FPCP |

0.1xxxx...xxxx 0.0xxxx...xxxx xxxxx...xxxx 11111...1111 |

| Intervalles approximatives | |

|---|---|

| Valeur maximale positive normalisée | 3.4 × 1038 |

| Minimum positif normalisé | 1.2 × 10-38 |

| Minimum positif dénormalisé | 1.4 × 10-45 |

Résumé du format réel double précision :

| Taille du champ en bits | |

|---|---|

| Signe(s) | 1 |

| Exposant biaisé (e) | 11 |

| Fraction (f) | 52 |

| Total | 64 |

| Interprétation du signe | |

|---|---|

| Fraction positive | s = 0 |

| Fraction négative | s = 1 |

| Nombres normalisés | |

|---|---|

| Biais de l'exposant biaisé | +1023 ($3FF) |

| Intervalle d'exposants biaisés | 0 < e < 2047 ($7FF) |

| Intervalle de fractions | Zéros ou non zéros |

| Fraction | 1.f |

| Relation avec la représentation des nombres réels | (-1)s × 2e-1023 × 1.f |

| Nombres dénormalisés | |

|---|---|

| Format d'exposant biaisé minimum | 0 ($000) |

| Biais de l'exposant biaisé | +1022 ($3FE) |

| Intervalle de fraction | Non zéro |

| Fraction | 0.f |

| Relation avec la représentation des nombres réels | (-1)s × 2-1022 × 0.f |

| Zéros signés | |

|---|---|

| Format d'exposant biaisé minimum | 0 ($00) |

| Fraction (Mantisse/Significande) | 0.f = 0.0 |

| Infinis signés | |

|---|---|

| Format d'exposant biaisé maximum | 2047 ($7FF) |

| Fraction | 0.f = 0.0 |

| NAN | |

|---|---|

| Signe | 0 ou 1 |

| Format d'exposant biaisé maximum | 255 ($7FF) |

| Fraction | Non zéro |

| Représentation d'une fraction Sans signalisation Avec signalisation Motif binaire non nul créé par l'utilisateur Fraction générée par FPCP |

1xxxx...xxxx 0xxxx...xxxx xxxxx...xxxx 11111...1111 |

| Intervalles approximatives | |

|---|---|

| Valeur maximale positive normalisée | 18 × 10308 |

| Minimum positif normalisé | 2.2 × 10-308 |

| Minimum positif dénormalisé | 4.9 × 10-324 |

Résumé du format réel à précision étendue :

| Taille du champ en bits | |

|---|---|

| Signe(s) | 1 |

| Exposant biaisé (e) | 15 |

| Zéro, réservé (u) | 16 |

| Bit entier explicite (j) | 1 |

| Mantisse (f) | 63 |

| Total | 96 |

| Interprétation des bits inutilisés | |

|---|---|

| Entrée | Indifférent |

| Sortie | Zéros |

| Interprétation du signe | |

|---|---|

| Mantisse positive | s = 0 |

| Mantisse négative | s = 1 |

| Nombres normalisés | |

|---|---|

| Biais de l'exposant biaisé | +16383 ($3FFF) |

| Intervalle d'exposants biaisés | 0 < = e < 32767 ($7FFF) |

| Bit entier explicite | 1 |

| Intervalle de valeurs de la mantisse | Zéro ou non zéro |

| Mantisse (bit entier explicite et fraction) | 1.f |

| Relation avec la représentation des nombres réels | (-1)s × 2e-16383 × 1.f |

| Nombres dénormalisés | |

|---|---|

| Format d'exposant biaisé minimum | 0 ($0000) |

| Biais de l'exposant biaisé | +16383 ($3FFF) |

| Bit entier explicite | 0 |

| Intervalle de valeurs de Mantisse | Non zéro |

| Mantisse (bit entier explicite et fraction) | 0.f |

| Relation avec la représentation des nombres réels | (-1)s × 2-16383 × 0.f |

| Zéros signés | |

|---|---|

| Format d'exposant biaisé minimum | 0 ($0000) |

| Mantisse (bit entier explicite et fraction) | 0.0 |

| Infinis signés | |

|---|---|

| Format d'exposant biaisé maximum | 32767 ($7FFF) |

| Bit entier explicite | Indifférent («Je m'en fiche») |

| Mantisse (bit entier explicite et fraction) | x.000...0000 |

| NAN | |

|---|---|

| Signe | Indifférent («Je m'en fiche») |

| Bit entier explicite | Indifférent («Je m'en fiche») |

| Format d'exposant biaisé maximum | 32767 ($7FFF) |

| Mantisse | Non-zéro |

| Représentation de la fraction Non-signalisation Signalisation Motif binaire non nul créé par l'utilisateur Fraction lors de la création par FPCP |

x.1xxxx...xxxx x.0xxxx...xxxx x.xxxxx...xxxx 1.11111...1111 |

| Intervalle approximatives | |

| Valeur maximale positive normalisée | 1.2 × 104932 |

| Minimum positif normalisé | 1.7 × 10-4932 |

| Minimum positif dénormalisé | 3.7 × 104951 |

Résumé du format décimal réel compressé :

| Type de données | SM | SE | Y | Y | Exposant à 3 chiffres | Entier à 1 chiffre | Fraction à 16 chiffres |

|---|---|---|---|---|---|---|---|

| ±Infini | 0/1 | 1 | 1 | 1 | $FFF | $XXXX | $00...00 |

| ±NAN | 0/1 | 1 | 1 | 1 | $FFF | $XXXX | Non-zéro |

| ±SNAN | 0/1 | 1 | 1 | 1 | $FFF | $XXXX | Non-zéro |

| +Zéro | 0 | 0/1 | X | X | $000-$999 | $XXX0 | $00...00 |

| -Zéro | 1 | 0/1 | X | X | $000-$999 | $XXX0 | $00...00 |

| +Dans l'intervalle | 0 | 0/1 | X | X | $000-$999 | $XXX0-$XXX9 | $00...01-$99...99 |

| -Dans l'intervalle | 1 | 0/1 | X | X | $000-$999 | $XXX0-$XXX9 | $00...01-$99...99 |

Un format de données réelles décimales compactées, avec les bits SE et Y à 1, un exposant $FFF et une fraction décimale non nulle sur 16 bits, représente un NaN. Lorsque l'unité de calcul en virgule flottante (FPU) utilise ce format, la fraction du NaN est déplacée bit par bit dans la mantisse à précision étendue d'un registre de données à virgule flottante. L'exposant du registre est positionné pour indiquer un NaN, et aucune conversion n'est effectuée. Le bit de poids fort (MSB) du chiffre le plus significatif de la fraction décimale (le MSB du chiffre 15) est indifférent, comme pour les NaN à précision étendue, et le MSB du chiffre 15 moins un est le bit SNAN. Si le bit NaN est à zéro, il s'agit d'un SNAN.

Si un chiffre non décimal ($A - $F) apparaît dans l'exposant d'un zéro, le nombre est un zéro. L'unité de calcul en virgule flottante (FPU) ne détecte pas les chiffres non décimaux dans l'exposant, la partie entière ou la partie fractionnaire d'un format de données réelles décimales compactées. Ces chiffres non décimaux sont convertis en binaire de la même manière que les chiffres décimaux ; cependant, le résultat est probablement inutilisable, bien que reproductible. Puisqu'un nombre dans l'intervalle autorisée ne peut pas subir de dépassement de capacité lors de sa conversion en précision étendue, la conversion à partir du format de données réelles décimales compactées produit toujours des nombres normalisés en précision étendue.

Organisation des données dans les registres

Les paragraphes suivants décrivent l'organisation des données au sein des registres de données, d'adresses et de contrôle.

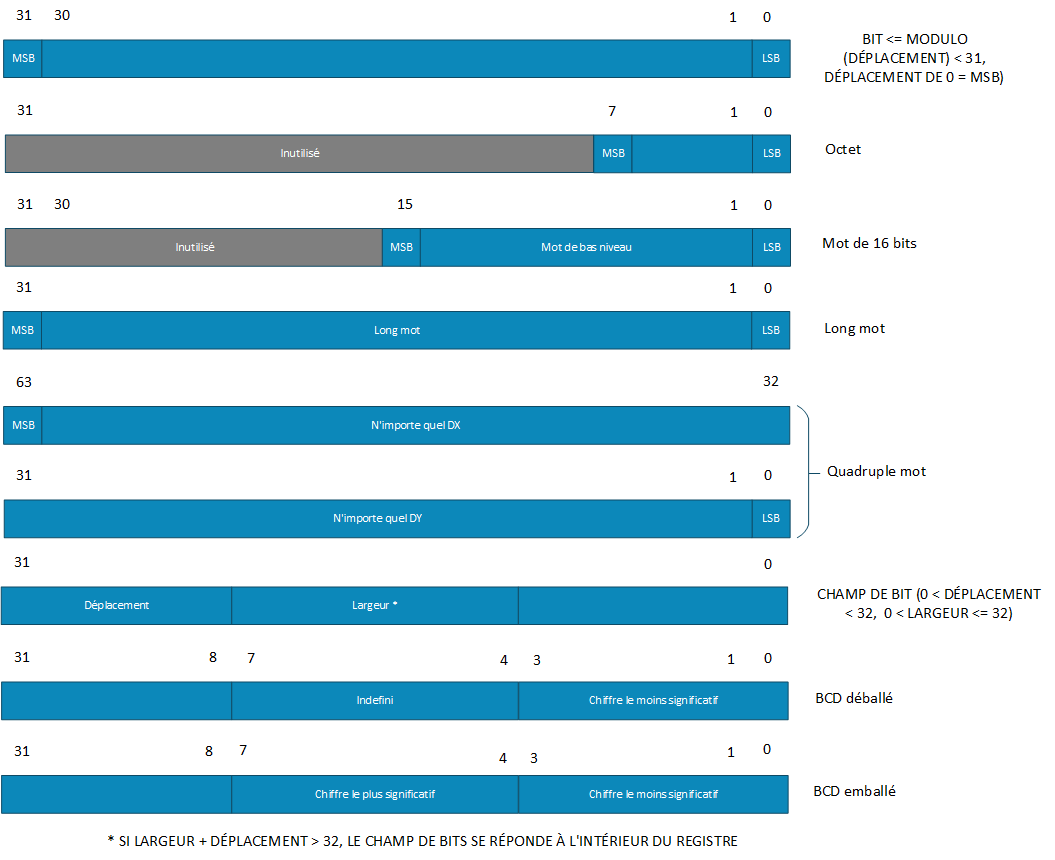

Organisation des formats de données entières dans les registres

Chaque registre de données entières est codé sur 32 bits. Les opérandes de type octet et mot occupent respectivement les 8 et 16 bits de poids faible des registres de données entières. Les opérandes de type mot long occupent la totalité des 32 bits des registres de données entières. Un registre de données, qu'il soit source ou destination, n'utilise ou ne modifie que les 8 ou 16 bits de poids faible appropriés (pour les opérations sur octet ou mot, respectivement). La partie de poids fort restante est inchangée et inutilisée. L'adresse du bit de poids faible (LSB) d'un entier de type mot long est zéro, et le bit de poids fort (MSB) est 31. Pour les champs de bits, l'adresse du MSB est zéro, et le LSB est égal à la largeur du registre moins un (le décalage). Si la largeur du registre plus le décalage est supérieure à 32, le champ de bits est tronqué à l'intérieur du registre. La figure 1-18 illustre l'organisation des différents formats de données dans les registres de données.

Un exemple de mot quadruple est le produit d'une multiplication 32 bits ou le quotient d'une division 32 bits (signée ou non signée). Les mots quadruples peuvent être organisés dans deux registres de données entiers quelconques, sans restriction d'ordre ni d'appariement. Il n'existe pas d'instructions explicites pour la gestion de ce format de données, bien que l'instruction MOVEM permette de déplacer un mot quadruple dans ou hors des registres.

Les données en décimal codé binaire (BCD) représentent les nombres décimaux sous forme binaire. Bien qu'il existe de nombreux codes BCD, les instructions BCD de la famille M68000 prennent en charge deux formats : compacté et non compacté. Dans ces formats, les bits de poids faible (LSB) contiennent un nombre binaire dont la valeur numérique correspond au nombre décimal. En format BCD non compacté, un octet définit un nombre décimal dont les quatre LSB contiennent la valeur binaire et les quatre MSB sont indéfinis. Chaque octet du format BCD compacté contient deux nombres décimaux. Les quatre bits de poids faible contiennent le nombre décimal de poids faible et les quatre bits de poids fort contiennent le nombre décimal de poids fort.

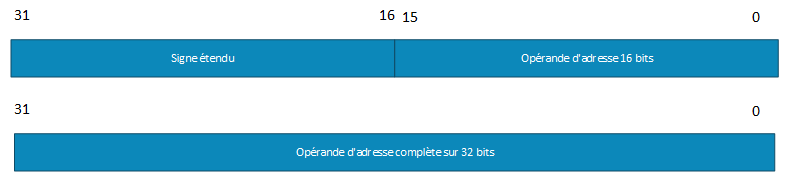

Les registres d'adresse et les pointeurs de pile étant codés sur 32 bits, ils ne peuvent pas être utilisés pour des opérandes de la taille d'un octet. Lorsqu'un registre d'adresse est l'opérande source, seul le mot de poids faible ou l'opérande entier (mot long) est utilisé, selon la taille de l'opération. Lorsqu'un registre d'adresse est l'opérande de destination, c'est le registre entier qui est affecté, quelle que soit la taille de l'opération. Si l'opérande source est de la taille d'un mot, il est étendu à 32 bits avant d'être utilisé dans l'opération vers un registre d'adresse de destination. Les registres d'adresse servent principalement à la gestion des adresses et au calcul des adresses. Le jeu d'instructions comprend des instructions permettant d'ajouter, de comparer et de déplacer le contenu des registres d'adresse. La figure suivante illustre l'organisation des adresses dans les registres d'adresse.

La taille des registres de contrôle varie selon leur fonction. Certains registres de contrôle comportent des bits non définis, réservés à une définition ultérieure par Motorola. Ces bits sont lus à zéro et doivent être écrits à zéro pour assurer la compatibilité future.

Toutes les opérations sur le SR et le CCR sont des opérations de la taille d'un mot. Pour toutes les opérations sur le CCR, l'octet de poids fort est lu à zéro et ignoré lors de l'écriture, même en mode privilégié. Les registres de code de fonction alternatifs, le code de fonction superviseur (SFC) et le code de fonction de données (DFC), sont des registres 32 bits dont seuls les bits 0P2 sont implémentés. Ces bits contiennent les valeurs d'espace d'adressage pour les opérandes de lecture ou d'écriture des instructions MOVES, PFLUSH et PTEST. Les valeurs sont transférées vers et depuis le SFC et le DFC à l'aide de l'instruction MOVEC. Il s'agit de transferts de mots longs ; les 29 bits de poids fort sont lus à zéro et ignorés lors de l'écriture.

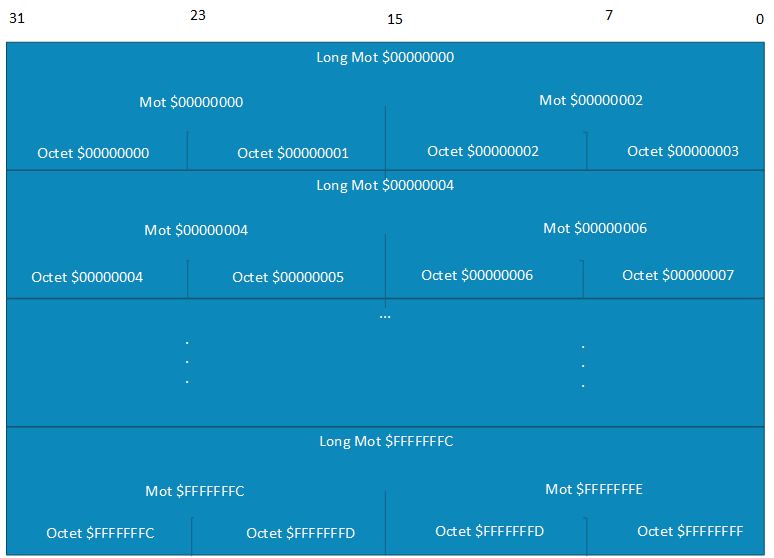

Organisation des formats de données entières en mémoire

L'organisation de la mémoire par adressage octet permet aux adresses les plus basses de correspondre aux octets de poids fort. L'adresse N d'un élément de données de type mot long correspond à l'adresse du bit de poids fort (MSB) du mot de poids fort. Le mot de poids faible se situe à l'adresse N + 2, le bit de poids faible (LSB) se trouvant à l'adresse N + 3 (voir figure suivante). L'organisation des formats de données en mémoire est conforme à celle de la famille M68000. L'adresse la plus basse (la plus proche de $00000000) correspond à l'emplacement du MSB, chaque LSB suivant se trouvant à l'adresse suivante (N + 1, N + 2, ...). L'adresse la plus élevée (la plus proche de $FFFFFFFF) correspond à l'emplacement du LSB.

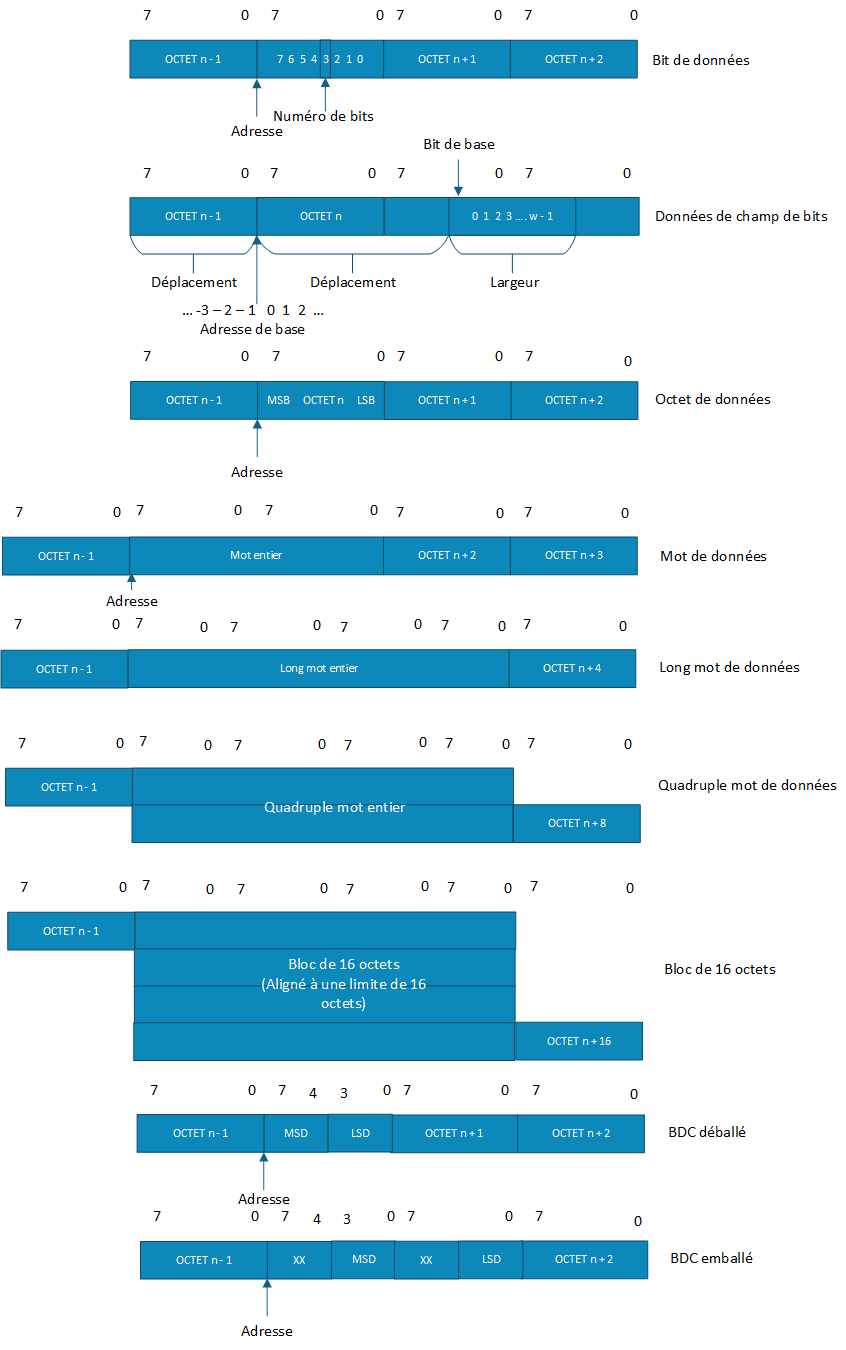

La figure suivante illustre l'organisation des formats de données IU en mémoire. Une adresse de base, sélectionnant un octet en mémoire (l'octet de base), spécifie un numéro de bit qui sélectionne un bit (l'opérande) dans cet octet de base. Le bit de poids fort (MSB) de l'octet est 7.

Les conditions suivantes spécifient un opérande de champ de bits :

- Une adresse de base sélectionnant un octet en mémoire.

- Un décalage de champ de bits qui indique la position du bit le plus à gauche (bit de base) du champ de bits par rapport au MSB de l'octet de base.

- Une largeur de champ de bits qui détermine le nombre de bits situés à droite du bit de base dans le champ de bits.

Le bit de poids fort (MSB) de l'octet de base correspond au décalage de champ de bits 0 ; le bit de poids faible (LSB) de l'octet de base correspond au décalage de champ de bits 7 ; et le bit de poids faible de l'octet précédent en mémoire correspond au décalage de champ de bits moins 1. Les décalages de champ de bits peuvent prendre des valeurs comprises entre 2 et 31 et 2³¹ moins 1, et la largeur des champs de bits peut varier de 1 à 32 bits.

Un opérande de bloc de 16 octets, pris en charge par l'instruction MOVE16, est un bloc de 16 octets aligné sur une limite de 16 octets. Cet opérande est spécifié par une adresse pouvant pointer vers n'importe quel octet du bloc.

Organisation des formats de données de l'unité de calcul en virgule flottante dans les registres et la mémoire

Les huit registres de données à virgule flottante de 80 bits sont analogues aux registres de données entières et sont entièrement génériques (c'est-à-dire que toute instruction peut utiliser n'importe quel registre). Le MC68040 ne prend en charge que certains formats et types de données au niveau matériel. Le tableau suivant répertorie les formats de données pris en charge par le MC68040 :

| Types de nombre | Formats des données | ||||||

|---|---|---|---|---|---|---|---|

| Nombre réel simple précision | Nombre réel double précision | Nombre réel à précision étendue | Nombre réel décimal compacté | Entier octet | Entier mot | Entier mot long | |

| Normalisé | * | * | * | † | * | * | * |

| Zéro | * | * | * | † | * | * | * |

| Infini | * | * | * | † | |||

| NAN | * | * | * | † | |||

| Dénormalisé | † | † | † | † | |||

| Non normalisé | † | † | |||||

Notes :

- * = Format/type de données pris en charge par le matériel FPU MC68040 intégré

- † = Format/type de données pris en charge par le logiciel (MC68040FPSP)

La figure suivante illustre le format des données à virgule flottante pour l'organisation des données réelles binaires en mémoire à simple, double et étendue précision :