Le microprocesseur 6502 du ORIC

Le microprocesseur 6502 du ORIC : Voici divers informations concernant le fonctionnement du microprocesseur 6502 qu'utilise l'ORC.

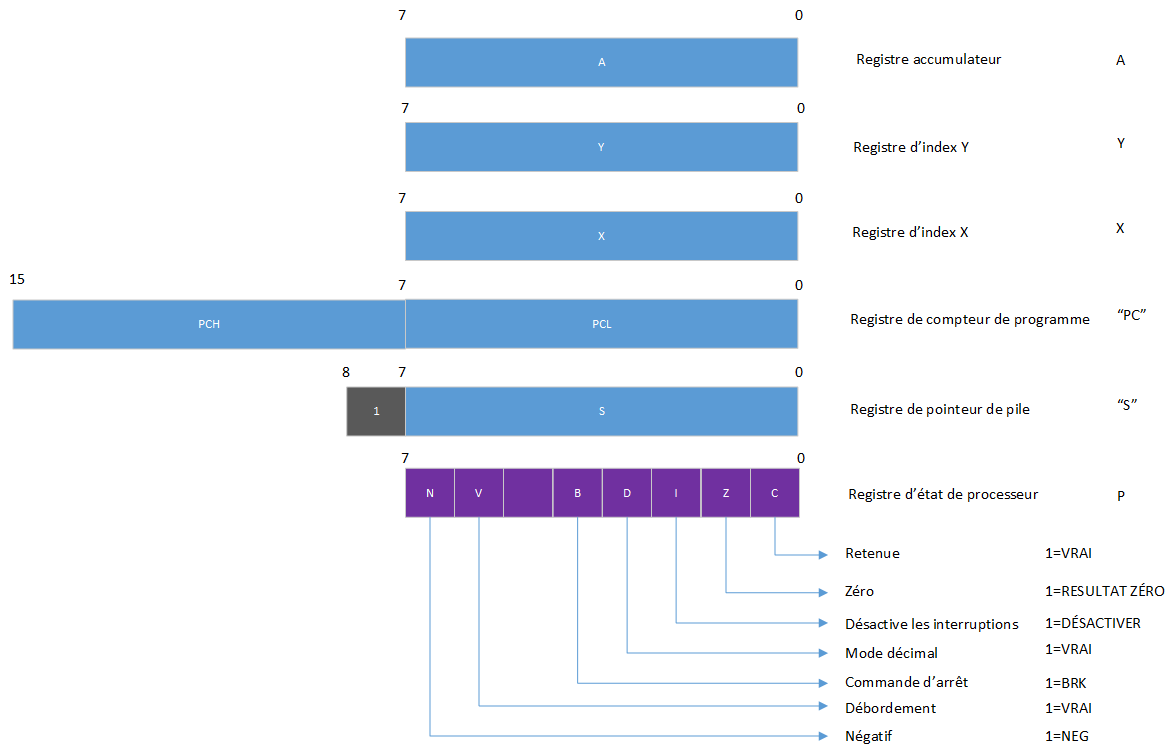

Modèle de programmation du processeur

Instructions machine

| Nom | Description |

|---|---|

| ADC | Ajouter de la mémoire à l'accumulateur |

| AND | Et binaire mémoire avec accumulateur |

| ASL | Décaler un bit vers la gauche (mémoire ou accumulateur) |

| BCC | Branchement sur retenue effacé |

| BCS | Branchement sur retenue fixé |

| BEQ | Branche sur le résultat zéro |

| BIT | Bits de test en mémoire avec accumulateur |

| BMI | Branche sur résultat moins |

| BNE | Branche sur résultat non zéro |

| BPL | Branche sur résultat plus |

| BRK | Force l'arrêt |

| BVC | Branche sur débordement effacé |

| BVS | Branche sur débordement fixé |

| CLC | Effacer le drapeau de retenue |

| CLD | Effacer le mode décimal |

| CLI | Effacer le bit de désactivation d'interruption |

| CLV | Effacer le drapeau de débordement |

| CMP | Comparer la mémoire et l'accumulateur |

| CPX | Comparer la mémoire et l'index X |

| CPY | Comparer la mémoire et l'index Y |

| DEC | Décrémenter la mémoire de un. |

| DEX | Décrémenter l'index X de un |

| DEY | Décrémenter l'index Y de un |

| EOR | Mémoire exclusive ou avec accumulateur |

| INC | Incrémenter la mémoire de un |

| INX | Incrémenter l'index X de un |

| INY | Incrémenter l'indice Y de un |

| JMP | Aller au nouvel emplacement |

| JSR | Accéder à la nouvelle adresse de retour de la chaîne d'emplacement |

| LDA | Accumulateur de charge avec mémoire |

| LDX | Charger l'index X avec de la mémoire |

| LDY | Charger l'index Y avec la mémoire |

| LSR | Décaler un bit vers la droite (mémoire ou accumulateur) |

| NOP | Pas d'opération |

| ORA | Ou binaire mémoire avec accumulateur |

| PHA | Pousser l'accumulateur sur la pile |

| PHP | Pousser l'état du processeur sur la pile |

| PLA | Extraire l'accumulateur de la pile |

| PLP | Extraire l'état du processeur de la pile |

| ROL | Rotation d'un bit vers la gauche (mémoire ou accumulateur) |

| ROR | Rotation d'un bit vers la gauche (mémoire ou accumulateur) |

| RTI | Retour d'interruption |

| RTS | Retour du sous-programme |

| SBC | Soustraire la mémoire de l'accumulateur avec la retenue |

| SEC | Fixe le drapeau de retenue |

| SED | Fixe le mode décimal |

| SEI | Fixe l'état de désactivation des interruptions |

| STA | Entrepose l'accumulateur en mémoire |

| STX | Entrepose l'index X en mémoire |

| STY | Entrepose l'index Y en mémoire |

| TAX | Transfère l'accumulateur vers l'index X |

| TAY | Transfère l'accumulateur vers l'index Y |

| TSX | Transfère le pointeur de pile vers l'index X |

| TXA | Transfère l'indice X dans l'accumulateur |

| TXS | Transfère l'index X vers le pointeur de pile |

| TYA | Transfère l'indice Y à l'accumulateur |

Codes d'instruction

| Nom/Description | Opération | Format de langage assembleur | Mode d'adressage | Nombre d'octets | Opcode hexadécimal | Codes de registres d'état de processeur |

|---|---|---|---|---|---|---|

| ADC Ajouter de la mémoire à l'accumulateur |

A·M·C → A.C. | ADC Oper ADC Oper ADC Oper.X ADC Oper ADC Oper.X ADC Oper.Y ADC (Oper.X) ADC (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 2 2 3 3 3 2 2 |

69 65 75 60 70 79 61 71 |

N V Z C |

| AND Et binaire mémoire avec accumulateur |

A∧M → | AND Oper AND Oper AND Oper AND Oper.X AND Oper.X AND Oper.Y AND (Oper.X) AND (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 2 2 3 3 3 2 2 |

29 25 35 20 30 39 31 31 |

N V |

| ASL Décaler un bit vers la gauche (mémoire ou accumulateur) |

ASL A ASL Oper ASL Oper.X ASL Oper ASL Oper.X |

Accumulateur Page zéro Page zéro.X Absolue Absolue X |

1 2 2 3 3 |

0A 06 16 0E 1E |

N Z C | |

| BCC Branchement sur retenue effacé |

Branche dans C=0 | BCC Oper | Relatif | 2 | 90 | |

| BCS Branchement sur retenue fixé |

Branche dans C=1 | BCS Oper | Relatif | 2 | 80 | |

| BEQ Branche sur le résultat zéro |

Branche dans Z=1 | BEQ Oper | Relatif | 2 | F0 | |

| BIT Bits de test en mémoire avec accumulateur |

A∧M M, → N, M, → V | BIT *Oper BIT * Oper |

Page zéro Absolue |

2 3 |

24 2C |

M7 M6 Z |

| BMI Branche sur résultat moins |

Branche dans N=1 | BMI Oper | Relatif | 2 | 30 | |

| BNE Branche sur résultat non zéro |

Branche dans Z=0 | BNE Oper | Relatif | 2 | D0 | |

| BPL Branche sur résultat plus |

Branche dans N=0 | BPL Oper | Relatif | 2 | 10 | |

| BRK Force l'arrêt |

Force l'interruption PC + 2 |P| |

BRK* | Implicite | 1 | 00 | B, I → 1 |

| BVC Branche sur débordement effacé |

Branche dans V=0 | BVC Oper | Relatif | 2 | 50 | |

| BVS Branche sur débordement fixé |

Branche dans V=1 | BVS Oper | Relatif | 2 | 70 | |

| CLC Effacer le drapeau de retenue |

0 → C | CLC | Implicite | 1 | 18 | C → 0 |

| CLD Effacer le mode décimal |

0 → D | CLD | Implicite | 1 | D8 | D → 0 |

| CLI Effacer le bit de désactivation d'interruption |

O → I | CLI | Implicite | 1 | 58 | I → 0 |

| CLV Effacer le drapeau de débordement |

O → V | CLV | Implicite | 1 | 88 | V → 0 |

| CMP Comparer la mémoire et l'accumulateur |

A - M | CMP Oper CMP Oper CMP Oper CMP Oper.X CMP Oper.X CMP Oper.Y CMP (Oper.X) CMP (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 22 3 3 3 2 2 |

C9 C5 D5 CD DD D9 C1 D1 |

N Z C |

| CPX Comparer la mémoire et l'index X |

X - M | CPX Oper CPX Oper CPX Oper |

Immédiat Page zéro Absolue |

2 2 3 |

E0 E4 EC |

N Z C |

| CPY Comparer la mémoire et l'index Y |

Y - M | CPY Oper CPY Oper CPY Oper |

Immédiat Page zéro Absolue |

2 2 3 |

C0 C4 CC |

N Z C |

| DEC Décrémenter la mémoire de un. |

M - I → M | DEC Oper DEC Oper.X DEC Oper DEC Oper.X |

Page zéro Page zéro.X Absolue Absolue.X |

2 2 3 3 |

C6 D6 CE DE |

N Z |

| DEX Décrémenter l'index X de un |

X - 1 → X | DEX | Implicite | 1 | CA | N Z |

| DEY Décrémenter l'index Y de un |

Y - 1 → Y | DEY | Implicite | 1 | 88 | N Z |

| EOR Mémoire exclusive ou avec accumulateur |

A V M → A | EOR Oper EOR Oper EOR Oper EOR Oper.X EOR Oper.X EOR Oper.Y EOR (Oper.X) EOR (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 22 3 3 3 2 2 |

49 45 55 40 50 59 41 41 |

N Z |

| INC Incrémenter la mémoire de un |

M + I → M | INC Oper INC Oper.X INC Oper INC Oper.X |

Page zéro Page zéro.X Absolue Absolue.X |

2 2 3 3 |

E6 F6 EE FE |

N Z |

| INX Incrémenter l'index X de un |

X + 1 → X | INX | Implicite | 1 | E8 | N Z |

| INY Incrémenter l'indice Y de un |

Y + 1 → Y | INY | Implicite | 1 | C8 | N Z |

| JMP Aller au nouvel emplacement |

(PC + 1) → PCL (PC + 2) → PCH |

JMP Oper JMP Oper |

Absolue Indirecte |

3 3 |

4C 6C |

|

| JSR Accéder à la nouvelle adresse de retour de la chaîne d'emplacement |

PC + 2| (PCX + 1) → PCL (PCX + 1) → PCL |

JSR Oper | Absolue | 3 | 20 | |

| LDA Accumulateur de charge avec mémoire |

M → | LDA Oper LDA Oper LDA Oper LDA Oper.X LDA Oper.X LDA Oper.Y LDA (Oper.X) LDA (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 22 3 3 3 2 2 |

A9 A5 B5 AD BD B9 A1 B1 |

N Z |

| LDX Charger l'index X avec de la mémoire |

M → X | LDX Oper LDX Oper LDX Oper,Y LDX Oper LDX Oper,Y |

Immédiat Page zéro Page zéro.Y Absolue Absolue.Y |

2 2 2 3 3 |

A2 A6 B6 AE BE |

N Z |

| LDY Charger l'index Y avec la mémoire |

M → Y | LDY Oper LDY Oper LDY Oper,X LDY Oper LDY Oper,X |

Immédiat Page zéro Page zéro.Y Absolue Absolue.Y |

2 2 2 3 3 |

A0 A4 B4 AC BC |

N Z |

| LSR Décaler un bit vers la droite (mémoire ou accumulateur) |

LSR A LSR Oper LSR Oper.X LSR Oper LSR Oper.X |

Accumulateur Page zéro Page zéro.X Absolue Absolue.X |

1 2 2 3 3 |

4A 46 56 4E 5E |

N C N → 0 |

|

| NOP Pas d'opération |

Pas d'opération | NOP | Implicite | 1 | EA | |

| ORA Ou binaire mémoire avec accumulateur |

A ∨ M → A | ORA Oper ORA Oper ORA Oper ORA Oper.X ORA Oper.X ORA Oper.Y ORA (Oper.X) ORA (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 22 3 3 3 2 2 |

09 05 15 00 1D 19 01 11 |

N Z |

| PHA Pousser l'accumulateur sur la pile |

A| | PHA | Implicite | 1 | 48 | |

| PHP Pousser l'état du processeur sur la pile |

P| | PHP | Implicite | 1 | 08 | |

| PLA Extraire l'accumulateur de la pile |

A| | PLA | Implicite | 1 | 68 | N Z |

| PLP Extraire l'état du processeur de la pile |

P| | PLP | Implicite | 1 | 28 | Restauré |

| ROL Rotation d'un bit vers la gauche (mémoire ou accumulateur) |

ROL A ROL Oper ROL Oper.X ROL Oper ROL Oper.X |

Accumulateur Page zéro Page zéro.X Absolue Absolue.X |

1 2 2 3 3 |

2A 26 36 2E 3E |

N Z C | |

| ROR Rotation d'un bit vers la gauche (mémoire ou accumulateur) |

ROR A ROR Oper ROR Oper.X ROR Oper ROR Oper.X |

Accumulateur Page zéro Page zéro.X Absolue Absolue.X |

1 2 2 3 3 |

6A 66 76 6E 7E |

N Z C | |

| RTI Retour d'interruption |

P ← (SP) SP ← SP + 1 PCb ← (SP) SP ← SP + 1 PCh ← (SP) SP ← SP + 1 |

RTI | Implicite | 1 | 40 | |

| RTS Retour du sous-programme |

RTS | Implicite | 1 | 60 | ||

| SBC Soustraire la mémoire de l'accumulateur avec la retenue |

SBC Oper SBC Oper SBC Oper.X SBC Oper SBC Oper.X SBC Oper.Y SBC (Oper.X) SBC (Oper).Y |

Immédiat Page zéro Page zéro X Absolue Absolue X Absolue Y (indirecte.X) (Indirecte).Y |

2 2 2 3 3 3 2 2 |

E9 E5 F5 ED FD F9 E1 E1 |

||

| SEC Fixe le drapeau de retenue |

C ← 1 | SEC | Implicite | 1 | 38 | C |

| SED Fixe le mode décimal |

D ← 1 | SED | Implicite | 1 | F8 | D |

| SEI Fixe l'état de désactivation des interruptions |

I ← 1 | SEI | Implicite | 1 | 78 | I |

| STA Entrepose l'accumulateur en mémoire |

STA Oper STA Oper,X STA Oper STA Oper,X STA Oper,Y STA (Oper,X) STA (Oper),Y |

Page zéro Page zéro,X Position absolue Position absolue,X Position absolue,Y Indirecte,X Indirecte,Y |

2 2 3 3 3 2 2 |

85 95 8D 9D 99 81 91 |

||

| STX Entrepose l'index X en mémoire |

STX Oper STX Oper,Y STX Oper |

Page zéro Page zéro,Y Position absolue |

2 2 3 |

86 96 8E |

||

| STY Entrepose l'index Y en mémoire |

STY Oper STY Oper,Y STY Oper |

Page zéro Page zéro,Y Position absolue |

2 2 3 |

84 94 8C |

||

| TAX Transfère l'accumulateur vers l'index X |

X ← A | TAX | Implicite | 1 | AA | |

| TAY Transfère l'accumulateur vers l'index Y |

Y ← A | TAY | Implicite | 1 | A8 | |

| TSX Transfère le pointeur de pile vers l'index X |

X ← S | TXA | Implicite | 1 | BA | |

| TXA Transfère l'indice X dans l'accumulateur |

X → A | TXA | Implicite | 1 | 8A | N Z |

| TXS Transfère l'index X vers le pointeur de pile |

X → S | TXS | Implicite | 1 | 9A | |

| TYA Transfère l'indice Y à l'accumulateur |

X → A | TYA | Implicite | 1 | 98 | N Z |

Dernière mise à jour : Mardi, le 7 mars 2023