Introduction

Le micro-ordinateur A3000 a été lancé en mai 1989, juste avant la gamme A4x0/1. Il a été conçu pour être un ordinateur bon marché avec une extension limitée et un clavier et un système combinés. Il avait un ARM2, RISCOS 2.00 et le MEMC1a. Une fois de plus, Acorn a omis le port RS232 pour économiser de l'argent et l'extension est limitée à un seul mini-podule et un seul podule externe. Il n'y a pas d'option de disque dur, sauf sur un module de contrôleur externe SCSI ou IDE. L'A3000 était le dernier "micro-ordinateur BBC" avec un logo BBC sur le clavier.

Fiche technique

Voici les caractéristiques du «A3000» de «Acorn» :

| Spécification | Description |

|---|---|

| Fabricant | Acorn |

| Modèle | A3000 |

| Date de fabrication | 1989 |

| Microprocesseur | ARM2 VL2333-QC ou ARM VL86C010-10QC cadencé à 8MHz |

| Contrôleur de mémoire | MEMC1a |

| Mémoire | 1 Mo extensible à 2 Mo, vitesse d'horloge à 8 MHz |

| Contrôleur vidéo | VIDC1a |

| Contrôleur d'entrée/sortie | IOC (VL2311-QCou VL86C410-10QC) |

| Unité de disquette | Citizen OSDC-65C |

| Podule 0 | Port utilisateur AKA12, mise à jour MIDI |

| Econet | Module Econet 0259,200 |

| Système d'exploitation | RISC OS 2 à RISC OS 3.11 |

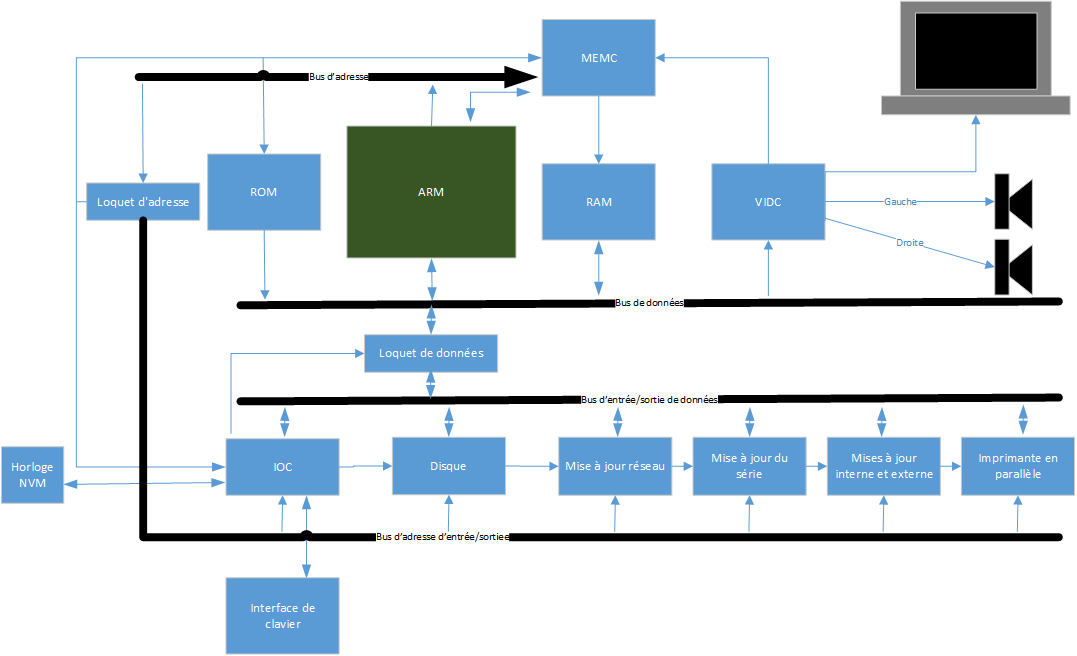

Architecture

L'ordinateur A3000 est construit autour de l'ensemble de puces ARM, comprenant le Acorn Risc Machine (ARM) elle-même, le contrôleur de mémoire MEMC (Memory Controller), le contrôleur vidéo VIDC (Video Controller) et le contrôleur d'entrée-sortie IOC (Input Output Controller). Un schéma fonctionnel de l'A3000 est présenté ci-dessous :

L'ARM IC est un microprocesseur à ensemble d'instructions réduit de 32 bits en pipeline acceptant les instructions et manipule les données via un bus de données 32 bits haute vitesse et un bus d'adresses 26 bits, offrant un espace d'adressage uniforme de 64 Mo. L'ARM prend en charge les systèmes de mémoire virtuelle en utilisant un ensemble d'instructions simple mais puissant avec une bonne prise en charge du compilateur de langage de haut niveau.

Le MEMC agit comme l'interface entre l'ARM, les contrôleurs vidéo et les entrées/sorties, la mémoire morte (ROM) et les périphériques de mémoire dynamique (DRAM), fournissant tous les signaux de synchronisation critiques du système, y compris les horloges du microprocesseur. De 1 à 2 Mo de DRAM sont connectés au MEMC fournissant tous les signaux et les opérations de rafraîchissement. Un convertisseur logique vers physique cartographie la mémoire physique dans un espace d'adressage logique de 32 Mo (avec trois niveaux de protection) permettant la mise en oeuvre des opérations de mémoire virtuelle et de multitâche. Les accès DRAM en mode page rapide sont utilisés pour maximiser la bande passante mémoire. Le VIDC demande des données à la RAM lorsque cela est nécessaire et les met en mémoire tampon dans l'une des trois FIFO avant de les utiliser. Les données sont demandées par blocs de quatre mots de 32 bits, ce qui permet une utilisation efficace de la DRAM en mode paginé sans verrouiller le bus de données système pendant de longues périodes. Le MEMC prend en charge les opérations d'accès direct à la mémoire (DMA) avec un ensemble de générateurs d'adresses DMA programmables fournissant une mémoire tampon circulaire pour les données vidéo, une mémoire tampon linéaire pour les données de curseur et une double mémoire tampon pour les données sonores.

Le contrôleur d'entrée-sortie (IOC) contrôle le bus d'entrée/sortie et les cartes d'extension et fournit des fonctions de base telles que l'interface clavier, les temporisateurs système, les masques d'interruption et les registres de contrôle. Il prend en charge un certain nombre de cycles périphériques différents et tous les accès entrées/sorties sont cartographiés en mémoire.

Le VIDC prend les données vidéo de la mémoire sous contrôle DMA, les sérialise et les transmet à une palette de recherche de couleurs, puis les convertit en signaux analogiques pour piloter les canons CRT. Le VIDC contrôle également tous les paramètres de synchronisation d'affichage et contrôle la position et le motif du sprite du curseur. De plus, il intègre un convertisseur numérique-analogique (DAC) exponentiel et une table d'images stéréo pour la génération d'un son de haute qualité à partir des données de la DRAM. Le VIDC est un appareil hautement programmable, offrant un très large choix de formats d'affichage. La palette de recherche de couleurs pilotant les trois DAC sur puce a une largeur de 13 bits, offrant un choix de 4096 couleurs ou une source vidéo externe. Le sprite du curseur mesure 32 pixels de large et n'importe quel nombre de rasters de haut. Trois couleurs simultanées (à nouveau parmi un choix de 4096) sont prises en charge et n'importe quel pixel peut être défini comme transparent, ce qui rend possibles les curseurs de nombreuses formes. Il peut être placé n'importe où sur l'écran.

Le système audio mis en oeuvre sur l'appareil peut prendre en charge jusqu'à 8 canaux, chacun avec une position stéréo distincte.

Le système d'entrée/sortie

Le système d'entrée/sortie est contrôlé par le contrôleur d'entrée/sortie (IOC) et le contrôleur de mémoire (MEMC). Le bus d'entrée/sortie prend en charge tous les périphériques internes et les cartes d'extension. Pour s'assurer que n'importe quel périphérique peut être branché dans n'importe quel emplacement, tous les codes de pilote pour les cartes d'extension doivent pouvoir être déplacés. Les références aux adresses des cartes d'extension directe ne doivent jamais être utilisées. Il appartient au système d'exploitation de la machine, conjointement avec l'ID de la carte d'extension, de déterminer l'adresse à laquelle une carte d'extension doit être accessible.

Architecture du système

Le système d'entrée/sortie (comprenant des cartes d'extension) se compose d'un bus de données 16 bits (BD[0:15]), d'un bus d'adresses tamponnées (LA[2:21]) et de divers signaux de contrôle et de synchronisation. Le bus de données d'entrée/sortie est indépendant du bus de données système principal à 32 bits, en étant séparé par des verrous et des tampons bidirectionnels. De cette façon, le bus de données d'entrée/sortie peut fonctionner à des vitesses beaucoup plus lentes que le bus système principal pour prendre en charge les périphériques plus lents. Les verrous entre les deux bus, et donc la synchronisation du bus d'entrée/sortie, sont contrôlés par IOC. Le IOC prend en charge 4 vitesses de cycle différentes (lente, moyenne, rapide et synchronisé).

Carte mémoire système

La carte de la mémoire système est définie par le MEMC a la composition suivante :

| Adresse hexadécimal | Lecture | Écriture |

|---|---|---|

| 3800000 à 3FFFFFF | ROM (haut) | Conversion d'adresse logique à physique |

| 3600000 à 3800000 | ROM (bas) | Générateur d'adresse DMA |

| 3400000 à 3600000 | Contrôleur vidéo | |

| 3000000 à 3400000 | Contrôleur d'entrée/sortie | |

| 2000000 à 3000000 | Cartographie physique de la RAM | |

| 0000000 à 2000000 | Cartographie logique de la RAM | |

Notez que tous les composants du système, y compris les périphériques d'entrée/sortie, sont cartographiés en mémoire.

Carte mémoire de l'espace d'entrée/sortie

Cet espace contrôlé par IOC a une allocation pour les cartes d'extension simples et les cartes d'extension MEMC.

Cartographie du bus de données

Le bus de données d'entrée/sortie a une largeur de 16 bits (8 bits pour l'interface de carte d'extension interne). Les accès bytewide sont utilisés pour les périphériques 8 bits. Le bus de données d'entrée/sortie (BD[0:15]) se connecte au bus de données système principal (D[0:31]) via un ensemble de verrous de données bidirectionnels.

Accès aux octets

Pour accéder aux cartes d'extension à l'échelle de l'octet, des instructions d'octet sont utilisées. Une instruction d'entreposage d'octet placera l'octet écrit sur les quatre octets du mot, et placera donc correctement la valeur souhaitée sur l'octet le plus bas du bus d'entrée/sortie. Un chargement d'octet ou de mot peut être utilisé pour lire une carte d'extension à l'échelle de l'octet dans l'octet le plus bas d'un registre ARM.

Accès à demi-mot

Pour accéder à une carte d'extension de 16 bits, des instructions à demi-mot sont utilisées. Lors de la mémorisation, le demi-mot est placé sur les 16 bits supérieurs, D[16:31]. Pour maintenir une compatibilité ascendante avec les futures machines, les mémoires de demi-mots reproduisent les données écrites sur le demi-mot inférieur, D[0:15]. Lors de la lecture, les 16 bits supérieurs sont indéfinis.

Identification de la carte d'extension

Il est important que le système puisse identifier quelles cartes d'extension (le cas échéant) sont présentes et où elles se trouvent. Cela se fait en lisant le ou les octets d'identification (PI) du podule (carte d'extension) dans le champ d'identification du podule.

Cartographie de la mémoire des adresses d'entrée/sortie

Tous les accès d'entrée/sortie sont cartographiés en mémoire. Le IOC est connecté comme détaillé dans ce tableau :

| IOC | ARM |

|---|---|

| CS | LA[21] |

| T[1] | LA[20] |

| T[0] | LA[19] |

| B(2] | LA[18] |

| B[1] | LA[17] |

| B[0] | LA[16] |

Carte de la mémoire du registre interne

| Adresse | Lecture | Écriture |

|---|---|---|

| 3200000H | Contrôle | Contrôle |

| 3200004H | Données série Rx | Données série Tx |

| 3200008H | - | - |

| 320000CH | - | - |

| 3200010H | État A du IRQ | - |

| 3200014H | Requête A du IRQ | Efface le IRQ |

| 3200018H | Masque A du IRQ | Masque A du IRQ |

| 320001CH | - | - |

| 3200020H | État B du IRQ | - |

| 3200024H | Requête B du IRQ | - |

| 3200028H | Masque B du IRQ | Masque B du IRQ |

| 320002CH | - | - |

| 3200030H | État du FIQ | - |

| 3200034H | Requête FIQ | - |

| 3200038H | Masque FIQ | Masque FIQ |

| 320003CH | - | - |

| 3200040H | Compte T0 Faible | Loquet T0 Bas |

| 3200044H | Compte T0 Élevé | Loquet T0 Haut |

| 3200048H | - | Aller à la commande T0 |

| 320004CH | - | Commande de locket T0 |

| 3200050H | Compte T1 Bas | Loquet T1 Bas |

| 3200054H | Compte T1 Haut | Loquet T1 Haut |

| 3200058H | - | Aller à la commande T1 |

| 320005CH | - | Commande de loquet T1 |

| 3200060H | Compte T2 Bas | Loquet T2 Bas |

| 3200064H | Compte T2 Haut | Loquet T2 Haut |

| 3200068H | - | Aller à la commande T2 |

| 320006CH | - | Commande de loquet T2 |

| 3200070H | Compteur de T3 bas | Loquet T3 Bas |

| 3200074H | Compte T3 haut | Loquet T3 haut |

| 3200078H | - | Aller à la commande T3 |

| 320007CH | - | Commande de loquet T3 |

Adresse de périphérique

| Type de cycle | Bk | Adresse de base | CI | Utiliser |

|---|---|---|---|---|

| Rapide | 1 | &3310000 | 1772 | Contrôleur d'unité de disquette |

| Synchronisé | 2 | &33A0000 | 6854 | Contrôleur Econet |

| Synchronisé | 3 | &3380000 | 6551 | Contrôleur de ligne série |

| Moyen | 5 | &32D0000 | HD63463 | Disque dur |

| Moyen | 5 | &32D0020 | HD63463 | Disque dur |

| Moyen | 5 | &32D0008 | HD63463 | Disque dur |

| Moyen | 5 | &32D0028 | HD63463 | Disque dur |

| Rapide | 5 | &3350010 | HC374 | Données d'imprimante |

| Rapide | 5 | &3350018 | HC574 | Loquet B |

| Rapide | 5 | &3350040 | HC574 | Loquet A |

| Rapide | 6 | - | - | Réservé |

| Lent | 4 | &3244000 | Podule | Expansion interne |

| Moyen | 4 | &32C4000 | Podule | Expansion interne |

| Rapide | 4 | &3344000 | Podule | Expansion interne |

| Synchronisé | 4 | &33C4000 | Podule | Expansion interne |

| Lent | 4 | &3240000 | Podule | Expansion externe |

| Moyen | 4 | &32C0000 | Podule | Expansion externe |

| Rapide | 4 | &3340000 | Podule | Expansion externe |

| Synchronisé | &33C0000 | Podule | Expansion externe | |

| Lent | 7 | &3270000 | Podule | Expansion externe étendue |