Introduction

Le contrôleur Intel 8259A de l'entreprise Intel est utilisé dans des micro-ordinateurs PC/XT et PC/AT ainsi que de nombreux micro-ordinateurs compatible au IBM PC afin de gérer le clavier, l'horloge et l'unité de disquette à l'aide des interruptions 08h à 0Fh (IRQ0 à IRQ7). Le contrôleur d'interruption programmable Intel 8259A gère jusqu'à 8 interruptions de priorité vectorisées pour le processeur simultanément. Il supporte jusqu'à 64 interruptions de priorité vectorisées sans circuits supplémentaires en cascade. Il est contenu dans un DIP à 28 broches, utilise la technologie NMOS et nécessite une seule alimentation +5V. Les circuits sont statiques, par conséquent, ils ne nécessitant aucune entrée d'horloge de la part d'un autre circuit. Le 8259A est conçu pour minimiser le temps système lors de la gestion des interruptions de priorité à plusieurs niveaux. Il a plusieurs modes, permettant l'optimisation pour une variété d'exigences du système. Le 8259A est entièrement compatible avec la puce Intel 8259. Les logiciels originalement écrit pour les puces 8259 utilisera le 8259A dans tous les modes équivalents 8259 (MCS-80/MCS-85, Non-Buffered, Edge Triggered).

Fiche technique

Voici les caractéristiques de la puce «8259A» de «Intel» :

| Spécification | Description |

|---|---|

| Fabricant | Intel |

| Modèle | 8259A |

| Date de conception | 1981 |

| Compatibilité | Intel 8086, Intel 8088, MCS-80, MCS-85 |

| Contrôleur | 8 niveaux ce priorité |

| Extensibilité | 64 niveaux |

| Programmation | Modes d'interruption programmable |

| Capacité | Masque de requête individuel |

| Modules | DIP de 28 broches ou PLCC de 28 broches |

| Alimentation | +5V (sans horloge) |

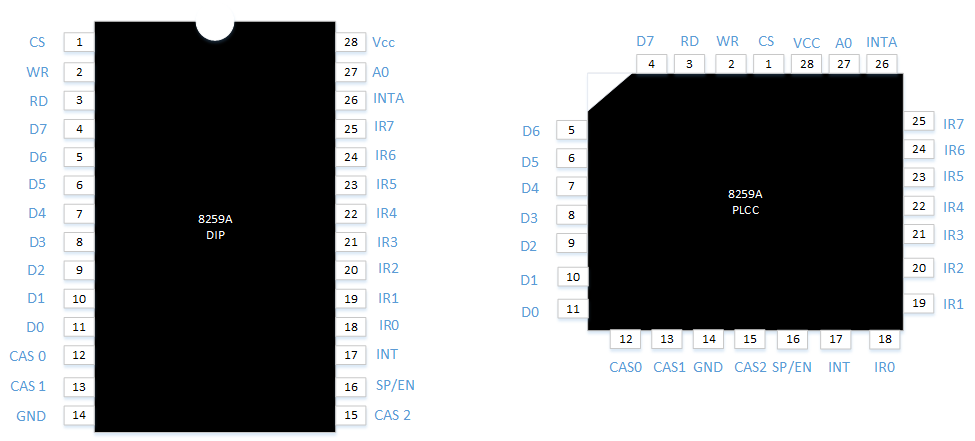

Schéma des broches

Voici le schéma des broches de la puce 8259A de l'entreprise Intel :

Voici la signification des broches de cette puce :

| Symbole | Broches | Type | Description |

|---|---|---|---|

| VCC | 28 | Entrée | ALIMENTATION : Cette broche fournit une alimentation de +5V. |

| GND | 28 | Entrée | PRISE DE TERRE : Cette broche fournit une prise vers la terre (Ground). |

| CS | 1 | Entrée | SELECTION DE PUCE : Cette broche permet d'activer les communications RD et WR entre le microprocesseur et le 8259A. Les fonctions INTA sont indépendantes de CS. |

| WR | 2 | Entrée | ECRITURE : Cette broche permet au 8259A d'accepter des mots de commande du microprocesseur. |

| RD | 3 | Entrée | LECTURE : Cette broche permet au 8259A de libérer un état sur le bus de données du microprocesseur. |

| D7 à D0 | 4 à 11 | Entrée/Sortie | BUS DE DONNÉES BIDIRECTIONNEL : Cette broche permet de contrôler les informations, l'état et le vecteur d'interruption. |

| CAS0 à CAS2 | 12, 13, 15 | Entrée/Sortie | LIGNE EN CASCADE : Cette broche permet de fournir un bus privé 8259A pour contrôler une structure multiple 8259A. Ces broches sont des sorties pour un maître 8259A et des entrées pour un esclave 8259A. |

| SP/EN | 16 | Entrée/Sortie | ESCLAVE DU PROGRAMME/ACTIVE LE TAMPON : Cette broche permet, en mode tampon, de contrôler les émetteurs-récepteurs de mémoire tampon (EN). Lorsqu'il n'est pas en mode tampon, il est utilisé comme entrée pour désigner un maître (SP = 1) ou un esclave (SP = 0). |

| INT | 17 | Sortie | INTERRUPTION : Cette broche permet de devenir haute chaque fois qu'une demande d'interruption valide est affirmée. Il est utilisé pour interrompre le microprocesseur, il est donc connecté à la broche d'interruption du microprocesseur. |

| IR0 à IR7 | 18 à 25 | Entrée | DEMANDE D'INTERRUPTION : Cette broche permet de demander d'exécuter une interruption en élevant une entrée IR (faible à élevée) et en la maintenant haute jusqu'à ce qu'elle soit acquittée (mode Edge Triggered), ou tout simplement par un niveau élevé d'une entrée IR (Level Triggered Mode). |

| INTA | 26 | Entrée | REPONSE D'INTERRUPTION : Cette broche permet d'activer les données de vecteur d'interruption 8259A sur le bus de données par une séquence d'impulsions d'acquittement d'interruption émises pour le microprocesseur. |

| A0 | 27 | Entrée | LIGNE D'ADRESSE A0 : Cette broche agit conjointement avec les broches CS, WR et RD. Il est utilisé par le 8259A pour déchiffrer divers mots de commande écrits par le microprocesseur et l'état qu'elle souhaite lire. Il est généralement connecté à la ligne d'adresse du microprocesseur A0 (A1 pour les microprocesseur 8086 et 8088). |

Interruptions dans les systèmes de micro-ordinateur

La conception du système de micro-ordinateur exige que les périphériques d'entrée/sortie comme que les claviers, les écrans, les capteurs et autres composants soient correctement traités, de sorte que le micro-ordinateur assume une grande partie des tâches système sans affecter le débit.

La méthode la plus courante de service de tels périphérique est l'approche Polled. C'est là que le processeur doit tester chaque périphérique en séquence et en effet «demander» à chacun s'il a besoin d'un service. Il est facile de voir qu'une grande partie du programme principal parcourt ce cycle de sondage continu et qu'une telle méthode aurait un effet néfaste sur le débit du système, limitant ainsi les tâches pouvant être assumée par le micro-ordinateur et réduire la rentabilité de l'utilisation de tels dispositifs.

Une méthode plus souhaitable serait celle permettant au microprocesseur d'exécuter son programme principal et de ne s'arrêter que pour le service des périphériques lorsque le dispositif lui-même le lui demande. En effet, la méthode fournirait une entrée désynchronisé externe informant le processeur qu'il devrait terminer toute instruction en cours d'exécution et récupérer une nouvelle routine allant desservir le périphérique demandeur. Toutefois, une fois cette opération terminée, le processeur reprend exactement là où il s'était arrêté.

Cette méthode est appelée une «Interruption». Il est facile de voir que le débit du système augmenterait considérablement et que le micro-ordinateur pourrait donc assumer davantage de tâches pour améliorer encore sa rentabilité.

Le contrôleur d'interruption programmable (PIC) fonctionne comme un gestionnaire global dans un environnement système piloté par les interruptions. Il accepte les demandes provenant de l'équipement de périphérique, détermine laquelle des demandes entrantes est de la plus haute importance (priorité), détermine si la demande entrante a une valeur de priorité plus élevée que le niveau en cours de traitement et émet un signal d'interruption au CPU basée sur son état.

Chaque périphérique ou structure a généralement un programme spécial ou une «routine» associée à ses besoins fonctionnels ou opérationnels spécifiques; c'est ce qu'on appelle une «routine de service». Le PIC, après l'émission d'une interruption au CPU, doit envoyer des informations vers la CPU permettant de de faire pointer le compteur de programme vers la routine de service associée au dispositif demandeur. Ce pointeur est une adresse dans une table de vectorisation (données vectorielles).

Le 8259A est un périphérique spécialement conçu pour être utilisé dans des systèmes de micro-ordinateurs pilotés par interruption en temps réel. Il gère 8 niveaux ou demandes et dispose de fonctionnalités intégrées pour l'extensibilité vers d'autres puces 8259A (jusqu'à 64 niveaux). Il est programmé par le logiciel du système en tant que périphérique d'entrée/sortie. Une sélection de modes de priorité est disponible pour le programmeur afin que la manière dont les demandes sont traitées par le 8259A puisse être configurée pour correspondre à ses exigences système. Les modes prioritaires peuvent être modifiés ou reconfigurés dynamiquement à tout moment par le programme principal. Cela signifie que la structure d'interruption complète peut être définie en fonction de l'environnement système au complet.

Registre de demande d'interruption (IRR) et registre de service (ISR)

Les interruptions sur les broches d'entrée IR sont gérées par 2 registres en cascade, le registre des demandes d'interruption (IRR) et le service en cours (ISR). L'IRR est utilisé pour entreposer tous les niveaux d'interruption demandant un service; et l'ISR est utilisé pour entreposer tous les niveaux d'interruption étant en cours de service.

Résolveur de priorité

Ce bloc logique détermine les priorités des bits définis dans l'IRR. La priorité la plus élevée est sélectionnée et envoyée dans le bit correspondant de l'ISR pendant l'impulsion INTA.

Registre de masque d'interruption (IMR)

L'IMR entrepose les bits masquant les lignes d'interruption à masquer. L'IMR fonctionne sur l'IRR. Le masquage d'une entrée de priorité supérieure n'affecte pas les lignes de demande d'interruption de qualité inférieure.

Interruption (INT)

Cette sortie va directement à l'entrée d'interruption du microprocesseur. Le niveau VOH sur cette broche est conçu pour être entièrement compatible avec les niveaux d'entrée des microprocesseurs 8080A, 8085A et 8086.

Interruption acceptée (INTA)

Les impulsions INTA amèneront le 8259A à libérer des informations de vectorisation sur le bus de données. Le format de ces données dépend du mode système (mPM) de la puce 8259A.

Tampon de bus de données

Ce tampon bidirectionnel à 8 bits à 3 états est utilisé pour interfacer le 8259A avec le bus de données du système. Les mots de contrôle et les informations d'état sont transférés via le tampon de bus de données.

Logique de lecture / écriture de contrôle

La fonction de ce bloc est d'accepter les commandes de sortie (OUT) du microprocesseur. Il contient les registres ICW (Initialization Command Word) et les registres OCW (Operation Command Word) entreposant les différents formats de contrôle pour le fonctionnement du périphérique. Ce bloc de fonction permet également de transférer l'état du 8259A sur le bus de données.

Sélection de puce (CS)

Un signal LOW sur cette entrée active la puce 8259A. Aucune lecture ou écriture de la puce n'aura lieu à moins que le périphérique ne soit sélectionné.

Écriture (WR)

Un LOW sur cette entrée permet au microprocesseur d'écrire des mots de contrôle (ICW et OCW) sur le 8259A.

Lecture (RD)

Un LOW sur cette entrée permet au 8259A d'envoyer l'état du registre de demande d'interruption (IRR), du registre de service en cours (ISR), du registre de masque d'interruption (IMR) ou du niveau d'interruption sur le bus de données.

A0

Ce signal d'entrée est utilisé conjointement avec les signaux WR et RD pour écrire des commandes dans les différents registres de commande, ainsi que pour lire les divers registres d'état de la puce. Cette broche peut être liée directement à l'une des broches d'adresse.

Le tampon/comparateur de cascade

Ce bloc de fonction entrepose et compare les identifiants de tous les 8259A utilisés dans le système. Les 3 broches d'entrée/sortie associées (CAS0 à 2) sont des sorties lorsque le 8259A est utilisé en tant que maître et des entrées lorsque le 8259A est utilisé en tant qu'esclave. En tant que maître, le 8259A envoie l'identificateur du dispositif esclave s'interrompant sur les lignes CAS0 à 2. L'esclave ainsi sélectionné enverra son adresse de sous-programme préprogrammée sur le bus de données pendant les une ou deux impulsions INTA suivantes.

Séquence d'interruption

Les fonctionnalités d'alimentation du 8259A dans un système de micro-ordinateur sont sa programmabilité et sa capacité d'adressage de routine d'interruption. Ce dernier permet de sauter directement ou indirectement à la routine d'interruption spécifique demandée sans interrogation des dispositifs d'interruption. La séquence normale des événements pendant une interruption dépend du type du microprocesseur utilisé. Les événements se produisent comme suit dans un système MCS-80 ou MCS-85 :

- Une ou plusieurs des broches DEMANDE D'INTERRUPTION (IR7 à IR0) sont élevées, réglant le ou les bits IRR correspondants.

- Le 8259A évalue ces demandes et envoie un INT au microprocesseur, le cas échéant.

- Le microprocesseur traite l'INT et répond par une impulsion INTA.

- Lors de la réception d'un INTA du groupe du microprocesseur, le bit ISR de priorité la plus élevée est défini et le bit IRR correspondant est réinitialisé. Le 8259A libérera également un code d'instruction CALL (11001101) sur le bus de données à 8 bits via ses broches D7 à D0.

- L'instruction CALL initiera 2 autres impulsions INTA à envoyer au groupe 8259A.

- Les 2 impulsions INTA permettent au 8259A de libérer son adresse de sous-programme préprogrammée sur le bus de données. L'adresse inférieure de 8 bits est libérée à la première impulsion INTA et l'adresse supérieure à 8 bits est libérée à la deuxième impulsion INTA.

- Il termine l'instruction CALL de 3 octets publiée par le 8259A. En mode AEOI, le bit ISR est réinitialisé à la fin de la troisième impulsion INTA. Sinon, le bit ISR reste activé jusqu'à ce qu'une commande EOI appropriée soit émise à la fin de la séquence d'interruption.

Voir également

Langage de programmation - Assembleur 80x86 - Références des ports d'entrée/sortie des 80x86 - Port 0020h

Articles - Les géants de l'informatique - Intel