Introduction

Les microprocesseurs 16 bits de la série NEC V sont des bases de périphériques améliorées basées sur une architecture de type 8086/8088. Les modèles V20 et V30 sont des remplacements compatibles avec des broches directes pour les processeurs Intel 8088 et 8086 respectivement et sont largement utilisés dans les clones d'ordinateurs personnels compatibles IBM PC. En utilisant une génération d'adresses et une mise en pipeline améliorées des instructions, les périphériques V20 / V30 offrent une vitesse d'exécution 40% supérieure à celle des systèmes 8088/8086 utilisant la même fréquence d'horloge. Le jeu d'instructions est compatible avec celui du 8088/8086 mais a été amélioré par l'ajout d'un certain nombre de nouvelles instructions. Les versions V40 et V50 incluent une génération d'horloge à puce, trois compteurs / temporisateurs, un contrôleur de priorité d'interruption et des canaux DMA. Ces périphériques offrent des fonctionnalités similaires aux processeurs Intel 80188 et Intel 80186 respectivement.

Premier fabricant

Nippon Electric Co.

Périphérique disponible

| Modèle | Description |

|---|---|

| μPD70108 (V20) | Ce modèle est une version bus de données 8 bits. |

| μPD70116 (V30) | Ce modèle est une version bus de données 16 bits. |

| μPD70208 (V40) | Ce modèle est un V20 avec périphériques sur puce. |

| μPD70216 (V50) | Ce modèle est un V30 avec périphériques sur puce. |

| μPD70136 (V33) | Ce modèle est un V30 rapide avec bus d'adresses étendu. |

Architecture

L'architecture du V30 est une version améliorée de l'architecture 8086. La principale différence réside dans l'ajout de pipeline et d'autres améliorations de la logique interne visant à améliorer la vitesse d'exécution par rapport à celle d'un 8086 fonctionnant avec la même fréquence d'horloge.

Paquet

| Modèle | Description |

|---|---|

| V20 / V30 | DIL à 40 broches, boîtier plat à 52 broches ou PLCC à 44 broches |

| V33 | PGA 68 broches |

| V40/V50 | PLCC à 68 broches, PGA à 68 broches ou boîtier plat à 80 broches |

| V25/V35 | PLCC à 84 broches ou boîtier plat à 94 broches |

Connexions de broches

Pour le V20 et le V30, les connexions par broches sont directement compatibles avec les processeurs Intel 8088 et 8086 respectivement.

Exigences de puissance

Vcc +4,75 V à +5,25 V

Intervalle de température

0°C à +70°C

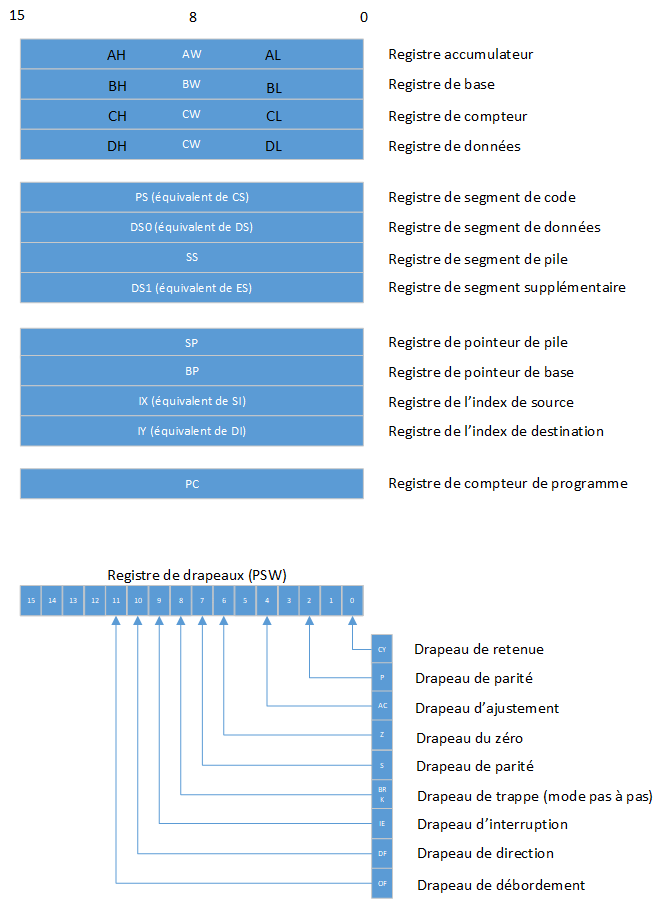

Registres des microprocesseurs

| MID | Nom | Description |

|---|---|---|

| AW | ACCUMULATOR | Registre accumulateur |

| BW | BASE REGISTER | Registre de base |

| CW | COUNTER REGISTER | Registre de compteur |

| DW | DATA REGISTER | Registre de données |

| IX | INDEX X | Registre d'index X |

| IY | INDEX Y | Registre d'index Y |

| SP | STACK POINTER | Registre de pointeur de pile |

| BP | BASE POINTER | Registre de pointeur de base |

| PS | PROGRAM SEGMENT | Registre de segment de programme |

| DS1 | DATA SEGMENT 1 | Registre de segment de données 1 |

| SS | STACK SEGMENT | Registre de segment de pile |

| DS0 | DATA SEGMENT 0 | Registre de segment de données 0 |

| PC | PROGRAM COUNTER | Registre de compteur de programme |

| PSW | STATUS WORD | Registre d'état de mot |

Installations d'interruption

Les processeurs V20/V30 peuvent gérer 256 exceptions différentes et leurs vecteurs sont conservés dans une table de vecteurs au bas de la mémoire. Chaque vecteur occupe 4 octets en mémoire, de sorte que la table de vecteurs complète occupe les 1 Ko inférieurs de mémoire. Les vecteurs sont alloués comme suit :

| Vecteur | Description |

|---|---|

| 0 | Erreur de division |

| 1 | Exception de débogage |

| 2 | NMI d'interruption non masqué |

| 3 | Interruption d'un octet INT |

| 4 | Interruption en cas de débordement INTO |

| 5 | Vérification de limites de tableaux BOUND |

| 6 | Opcode invalide |

| 7 | Périphérique non disponible |

| 8 | Double faute |

| 9 | Dépassement de segment de coprocesseur |

| 10 | TSS invalide |

| 11 | Segment non présent |

| 12 | Faute de pile |

| 13 | Faute de protection générale |

| 14 | Faute de page |

| 15 | Réservé |

| 16 | Erreur de coprocesseur |

| 17 à 32 | Réservé |

| 33 à 255 | Trappe d'instructions INT n |

Les instructions

L'ensemble d'instructions des processeurs de la série V est fondamentalement identique à celui des processeurs de type 8086/8088, à l'exception de quelques nouvelles instructions ayant été ajoutées. Les instructions de base fournies sur le V20 / V30 sont les suivantes :

| Instruction | Signification | Description |

|---|---|---|

| AAA | ASCII adjust AL after addition | Cette instruction permet d'adapter le résultat obtenu par l'addition de 2 valeur en format DCB. |

| AAD | ASCII adjust AX before division | Cette instruction permet de convertir une valeur de format DCB non compactée. |

| AAM | ASCII adjust AX after multiplication | Cette instruction offre la possibilité de convertir le produit de la multiplication de 2 valeurs de format DCB en un format DCB. |

| AAS | ASCII adjust AL after subtraction | Cette instruction permet d'adapter le résultat de la soustraction de nombre de format DCB. |

| ADC | Add with carry | Cette instruction additionne 2 quantités numériques sur 8 ou 16 bits et ajoute ensuite la valeur de l'indicateur de retenue, lequel est contenu dans le drapeau CF(CARRY FLAG), à la somme obtenu. |

| ADD | Add | Cette instruction additionne 2 quantités numérique sur 8, 16 ou 32 bits. |

| AND | And | Cette instruction permet d'effectuer un ET BINAIRE sur les 2 opérandes spécifiés. |

| CALL | Call procedure | Cette instruction force le microprocesseur à exécuter les instructions du sous-programme indiqué par l'adresse d'appel avant de continuer. |

| CBW | Convert byte to word | Cette instruction permet de convertir un nombre contenu dans le registre AL en un format sur 16 bits pour se retrouver dans le registre AX en appliquant une extension du signe. |

| CLC | Clear carry flag | Cette instruction permet de mettre l'indicateur d'état de retenu CF à 0. |

| CLD | Clear direction flag | Cette instruction met l'indicateur d'état DF à 0, soit la direction croissante. |

| CLI | Clear interrupt flag | Cette instruction met l'indicateur d'état IF à 0, soit l'interdiction des interruptions. |

| CMC | Complement carry flag | Cette instruction offre la possibilité d'inverser la valeur de l'indicateur de retenue. Si ce dernier vaut 1, elle le met à 0 et inversement. |

| CMP | Compare operands | Cette instruction offre la possibilité essentielle de comparer 2 registres ou emplacements de mémoire. |

| CMPS | Compare String | Cette instruction permet d'effectuer la comparaison d'un octet, d'un mot ou double mot spécifié avec l'opérande source et destination spécifié et fixe l'état des drapeaux du registres EFLAGS en fonction des résultats de la comparaison. |

| CWD | Convert word to doubleword | Cette instruction est l'alternative pour convertir le mot du registre AX en un double mot contenu dans le couple de registre DX et AX par extension du signe. |

| DAA | Decimal adjust AL after addition | Cette instruction corrige après coup les retenues lors de la manipulation de valeur DCB. |

| DEC | Decrement by 1 | Cette instruction décrément de 1 le registre ou l'adresse mémoire spécifié. |

| DIV | Unsigned divide | Cette instruction permet d'effectuer une division non-signée (nombre naturel). |

| HLT | Halt | Cette instruction permet de faire passer le microprocesseur en mode d'arrêt. Toutefois, le processeur peut quitter cet état lorsqu'une ligne matérielle RESET ou lorsqu'une interruption non-masquable (NMI) reçoit un signal. |

| IDIV | Integer divide | Cette instruction permet d'effectuer une division signée (nombre entier). |

| IMUL | Integer multiply | Cette instruction permet d'effectuer une multiplication signée (nombre entier). |

| IN | Input from port | Cette instruction permet de demander un octet, un mot ou un double mot provenant du port d'entrée/sortie et le retourne dans le registre accumulateur (AL, AX, EAX). |

| INC | Increment by 1 | Cette instruction permet d'incrémenter un registre ou un emplacement mémoire. |

| INS | Input from port to string | Cette instruction permet de demander un octet, un mot ou un double mot du port d'entrée/sortie et retourne le résultat dans l'adresse ES:[DI] et incrémente/décrémente le registre DI en fonction de la taille de l'opérande cible et de l'état du drapeau de direction. |

| INT | Interrupt | Cette instruction permet d'exécuter l'interruption avec le numéro spécifié. |

| INTO | Interrupt if overflow | Cette instruction permet d'exécuter l'interruption numéro 4 si le drapeau de débordement (OF) est fixé sur 1é |

| IRET | Return from interrupt | Cette instruction permet d'effectuer un retour précédemment provoquer par une interruption. |

| Jcc | Jump if condition | Ces instructions permettent d'effectuer d'effectuer un branchement conditionnel à emplacement mémoire spécifié. |

| JMP | Jump | Cette instruction permet d'effectuer un branchement à un emplacement mémoire spécifié. |

| LAHF | Load flags into AH register | Cette instruction permet de transférer les bits d'indicateurs du registre d'état vers le registre AH. |

| LDS | Load pointer using DS | Cette instruction permet de copier une adresse de mémoire contenu sur 32 bits dans la paire de registre de segment DS et dans un registre d'offset spécifié. |

| LEA | Load Effective Address | Cette instruction permet de copier l'offset d'une adresse de mémoire contenu dans un registre spécifié. |

| LEAVE | Leave stack frame | Cette instruction permet de libérer une zone de mémoire attribué par l'instruction «ENTER» lorsqu'on utilise des procédures dans des langages de programmation de haut niveau. |

| LES | Load ES with pointer | Cette instruction permet de copier une adresse de mémoire contenu sur 32 bits dans la paire de registre de segment ES et dans un registre d'offset spécifié. |

| LODS | Load String | Cette instruction permet de copier un élément de l'adresse DS:SI dans le registre accumulateur et incrémente/décrémente le registre SI en fonction de la taille de l'opérande source et de l'état du drapeau de direction. |

| LOOP | Loop | Cette instruction de boucle permet de décrémenter le registre CX (compteur de boucle) de 1 et par la suite de donner le contrôle à une étiquette destinataire tant que le registre CX ne vaut pas 0. |

| LOOPE | Loop equal | Cette instruction de boucle permet de décrémenter le registre CX (compteur de boucle) de 1 et par la suite de donner le contrôle à une étiquette destinataire tant que le registre CX ne vaut pas 0 et si le drapeau ZF vaut 1. |

| LOOPNE | Loop not equal | Cette instruction de boucle permet de décrémenter le registre CX (compteur de boucle) de 1 et par la suite de donner le contrôle à une étiquette destinataire tant que le registre CX ne vaut pas 0 et si le drapeau ZF vaut 0. |

| MOV | Move | Cette instruction permet de copier opérande source dans une opérande destinataire. |

| MOVS | Move String | Cette instruction permet de copier un élément de l'adresse DS:SI dans l'adresse ES:DI et incrémente/décrémente les registres DI et SI en fonction de la taille de l'opérande source et de l'état du drapeau de direction. |

| MOVSX | Move with sign-extend | Cette instruction permet de copier un registre de taille inférieur dans un registre de plus grande taille en remplissant les bits supplémentaires avec l'extension des signes. |

| MOVZX | Move with zero-extend | Cette instruction permet de copier un registre de taille inférieur dans un registre de plus grande taille en remplissant les bits supplémentaires par des 0. |

| MUL | Unsigned multiply | Cette instruction permet d'effectuer une multiplication non-signée (nombre naturel). |

| NEG | Negation | Cette instruction permet d'effectuer le complément à 2 d'une opérande. |

| NOP | No operation | Cette instruction ne fait rien. |

| NOT | Not | Cette instruction permet d'inverser la valeur de chacun des bits d'une opérande. |

| OR | Or | Cette instruction permet d'effectuer un OU BINAIRE sur les 2 opérandes spécifiés. |

| OUT | Output to port | Cette instruction permet d'envoyer un octet, un mot ou un double mot sur le port d'entrée/sortie. |

| OUTS | Output string to port | Cette instruction permet d'envoyer un octet, un mot ou un double mot contenu dans l'adresse DS:[SI] du port d'entrée/sortie et incrémente/décrémente le registre SI en fonction de la taille de l'opérande cible et de l'état du drapeau de direction. |

| POP | Pop data from stack | Cette instruction permet de désempiler de la pile une mot ou un double mot et la met dans une opérande. |

| POPA | Pop All | Cette instruction permet de désempiler de la pile respectivement les registres DI, SI, BP, SP, BX, DX, CX et AX. |

| POPF | Pop data into Flags register | Cette instruction permet de désempiler de la pile le registre 16 bits de drapeau contenant les indicateurs d'état. |

| PUSH | Push data onto stack | Cette instruction permet d'empiler une mot ou un double mot dans la pile. |

| PUSHA | Push All | Cette instruction permet d'empiler respectivement les registres DI, SI, BP, SP, BX, DX, CX et AX dans la pile. |

| PUSHF | Push flags onto stack | Cette instruction permet d'empiler respectivement le registre 16 bits de drapeau des indicateurs d'état dans la pile. |

| RCL 1 | Rotate left (with carry) | Cette instruction permet d'effectuer une rotation des bits vers la gauche en réinsérant le bit dans l'indicateur de retenue (CF) ainsi que dans le bit le plus à droite libéré. |

| RCR 1 | Rotate right (with carry) | Cette instruction permet d'effectuer une rotation des bits vers la droite en réinsérant le bit dans l'indicateur de retenue (CF) ainsi que dans le bit le plus à gauche libéré. |

| REP | Repeat | Cette instruction est utilisé comme préfixe avec d'autres instructions pour effectuer des répétitions d'instructions tant que CX ne vaut pas 0. |

| REPE | Repeat equal | Cette instruction est utilisé comme préfixe avec d'autres instructions pour effectuer des répétitions d'instructions jusqu'à ce que CX = 0 ou tant que l'indicateur ZF = 0. |

| REPNE | Repeat not equal | Cette instruction est utilisé comme préfixe avec d'autres instructions pour effectuer des répétitions d'instructions jusqu'à ce que CX = 0 ou tant que l'indicateur ZF = 1. |

| RET | Return from procedure | Cette instruction permet de quitter une procédure. |

| RETF | Return from far procedure | Cette instruction permet de quitter une procédure ayant lieu avec un appel long (FAR CALL). |

| RETN | Return from near procedure | Cette instruction permet de quitter une procédure ayant lieu avec un appel court (NEAR CALL). |

| ROL 1 | Rotate left | Cette instruction permet d'effectuer une rotation des bits vers la gauche en réinsérant le bit dans le bit le plus à droite libéré. |

| ROR 1 | Rotate right | Cette instruction permet d'effectuer une rotation des bits vers la droite en réinsérant le bit dans le bit le plus à gauche libéré. |

| SAHF | Store AH into flags | Cette instruction permet de copier les bits du registre AH dans l'octet de poids faible dans le registre des drapeaux (les indicateurs d'état). |

| SAL 1 | Shift Arithmetically left | Cette instruction permet d'effectuer une rotation des bits vers la gauche en réinsérant le bit dans l'indicateur de retenue (CF). |

| SAR 1 | Shift Arithmetically right | Cette instruction permet d'effectuer une rotation des bits vers la droite en réinsérant le bit dans l'indicateur de retenue (CF). |

| SBB | Subtraction with borrow | Cette instruction permet de soustraire avec l'indicateur de retenue (CF) une valeur à une opérande. |

| SCAS | String Compare String | Cette instruction permet de comparer un octet, un mot ou un double mot avec la cellule mémoire à l'adresse ES:[DI] et incrémente/décrémente le registre DI en fonction de la taille de l'opérande cible et de l'état du drapeau de direction. |

| SETcc | Set byte to one on condition | Cette directive permet de fixer la valeur d'une opérande 1 si la condition d'indicateur d'état du registre 32 bits de drapeau est vrai sinon fixe la valeur à 0. |

| SHL 1 | Shift left | Cette instruction permet d'effectuer une rotation des bits vers la gauche en réinsérant le bit dans l'indicateur de retenue (CF). |

| SHLD | Shift left double-word | Cette instruction permet d'effectuer une rotation des bits d'un double mot vers la gauche en réinsérant le bit dans l'indicateur de retenue (CF). |

| SHR 1 | Shift right | Cette instruction permet d'effectuer une rotation des bits vers la droite en réinsérant le bit dans l'indicateur de retenue (CF). |

| STC | Set carry flag | Cette instruction permet de fixer l'indicateur de retenue (CF) à la valeur 1. |

| STD | Set direction flag | Cette instruction permet de fixer l'indicateur de direction (DF) à la valeur 1. |

| STI | Set interrupt flag | Cette instruction permet de fixer l'indicateur d'interruption (IF) à la valeur 1. |

| STOS | Store in string | Cette instruction permet de copier un octet, un mot ou un double mot dans la cellule mémoire à l'adresse ES:[DI] et incrémente/décrémente le registre DI en fonction de la taille de l'opérande cible et de l'état du drapeau de direction. |

| SUB | Subtraction | Cette instruction permet de soustraire une valeur à une opérande. |

| TEST | Test | Cette instruction permet d'effectuer un «Et binaire» sur une opérande cible sans modifier sa valeur. |

| WAIT | Wait | Cette instruction permet de faire passer le microprocesseur en mode d'attente jusqu'à ce que la ligne de teste sur la carte mère s'active. |

| XCHG | Exchange | Cette instruction permet d'échanger la valeur de deux opérandes. |

| XLAT | Table look-up translation | Cette instruction permet de remplacer le contenu du registre AL par un octet de la «tablesource». |

| XOR | Exclusive OR | Cette instruction permet d'effectuer un OU exclusif BINAIRE sur les 2 opérandes spécifiés. |

Les nouvelles instructions disponibles sur les processeurs de la série V sont les suivantes :

| Instruction | Signification | Description |

|---|---|---|

| CLR1 | Clear a bit | Cette instruction permet d'effacer un bit. |

| NOT1 | Complement a bit | Cette instruction permet d'effectuer le complément d'un bit. |

| SET1 | Set a bit | Cette instruction permet de fixer d'un bit. |

| TEST1 | Test a bit | Cette instruction permet de tester un bit. |

| INS | Insert bit field | Cette instruction permet d'insérer un champ de bits. |

| EXT | Extract bit field | Cette instruction permet d'extraire le champ de bits. |

| ADD4S | Add BCD string | Cette instruction permet d'ajouter une chaîne de caractères BCD. |

| CMP4S | Compare BCD string | Cette instruction permet de comparer la chaîne de caractères BCD. |

| SUB4S | Substract BCD | Cette instruction permet de soustraire un BCD. |

| ROL4S | Rotate BCD string | Cette instruction permet d'effectuer la rotation vers la gauche de la chaîne de caractères BCD. |

| ROR4S | Rotate BCD string | Cette instruction permet d'effectuer la rotation vers la droite de la chaîne de caractères BCD. |

| POP R | Pop all registers | Cette instruction permet de dépiler tous les registres. |

| PUSH R | Push all registers | Cette instruction permet d'empiler tous les registres. |

| PUSH | Push immediate data | Cette instruction permet d'empiler des valeurs immédiates. |

| CHKIND | Check index | Cette instruction permet de vérifier l'index. |

| INM | Input string | Cette instruction permet d'entrée une chaîne de caractères. |

| OUTM | Output string | Cette instruction permet de sortir une chaîne de caractères. |

| REPC | Repeat if carry set | Cette instruction permet de répéter si le drapeau de retenu est fixé. |

| REPNC | Repeat if carry clear | Cette instruction permet de répéter si le drapeau de retenu est effacé. |