Les premiers pas

Le processeur MOS Technology 6502, commercialisé en 1975 au prix révolutionnaire de 25 dollars (contre environ 200 dollars pour les processeurs concurrents de l'époque), est un microprocesseur 8 bits ayant joué un rôle fondamental dans la révolution de la micro-informatique. Conçu par Chuck Peddle et son équipe chez MOS Technology, il est dérive conceptuellement du Motorola 6800, dont plusieurs des concepteurs du 6502 étaient les créateurs.

Le 6502 se distingue par :

- Une architecture 8 bits avec un bus de données de 8 bits

- Un bus d'adresses de 16 bits (espace adressable de 64 Ko)

- Un ensemble de registres minimaliste : un accumulateur (A), deux registres d'index (X et Y), un pointeur de pile (SP) et un registre d'état (P)

- 13 modes d'adressage, dont le puissant adressage par page zéro (zero page), offrant un accès rapide aux 256 premiers octets de la mémoire

- Un pipeline simplifie a 2 étages permettant un bon débit d'instructions malgré la simplicité du circuit

- Un ensemble de 56 instructions de base

- Un coût de fabrication extrêmement bas grâce a un nombre réduit de transistors (environ 3 510)

- Un fonctionnement a des fréquences de 1 a 3 MHz selon les variantes

Malgré sa simplicité apparente, le 6502 est remarquablement efficace. Son utilisation intensive de la page zéro comme un ensemble de pseudo-registres compense le faible nombre de registres internes, et ses modes d'adressage indirect permettent une manipulation flexible des pointeurs et des structures de données.

Variantes de la famille 6502

MOS Technology et ses licenseurs ont produit de nombreuses variantes du 6502 :

| Variantes | Description |

|---|---|

| 6502 | Version originale, 1 MHz (1975) |

| 6502A | Version améliorée, 2 MHz (1977) |

| 6502B | Version haute vitesse, 3 MHz (1982) |

| 6503 | Variante avec bus d'adresses réduit a 12 bits (4 Ko adressables), boîtier 28 broches |

| 6504 | Variante avec bus d'adresses réduit a 13 bits (8 Ko adressables), boîtier 28 broches |

| 6505 | Variante 28 broches, bus d'adresses 12 bits, pas de ligne RDY |

| 6507 | Variante 28 broches, bus d'adresses 13 bits, pas de lignes d'interruption (utilisée dans l'Atari 2600) |

| 6510 | Variante avec port d'entrée/sortie intégré de 6 bits, utilisée dans le Commodore 64 |

| 6512 | Version du 6502 compatible avec le bus du 6500/1 |

| 7501 | Variante utilisée dans le Commodore 16 et Plus/4 (procédé HMOS) |

| 8500 | Version HMOS du 6510, utilisée dans les Commodore 64C tardifs |

| 8502 | Variante cadencée a 2 MHz, utilisée dans le Commodore 128 |

Des versions CMOS améliorées ont été produites par d'autres fabricants :

| Versions CMOS | Description |

|---|---|

| 65C02 (WDC) | Version CMOS avec corrections de bugs et ajout de nouvelles instructions (BRA, PHX, PHY, PLX, PLY, STZ, TRB, TSB, BBR, BBS, RMB, SMB). Faible consommation. (1983) |

| 65SC02 | Version sans les instructions spécifiques Rockwell (BBR, BBS, RMB, SMB) |

| 65CE02 (CSG) | Version étendue avec registre Z supplémentaire, mode 16 bits partiel, et nouvelles instructions. Utilisée dans le Commodore 65 (prototype). |

| 65816 (WDC) | Extension 16 bits du 6502, retrocompatible. Bus d'adresses 24 bits (16 Mo). Utilisée dans le Super Nintendo (Ricoh 5A22) et l'Apple IIGS. |

| 65802 (WDC) | Version du 65816 compatible broche a broche avec le 6502 (bus d'adresses 16 bits seulement) |

| 2A03 (Ricoh) | Variante du 6502 sans mode BCD, avec générateur audio et contrôleur DMA intégrés, utilisée dans la Nintendo NES/Famicom |

| 2A07 (Ricoh) | Version PAL du 2A03 |

Toutes les variantes de la famille partagent l'ensemble d'instructions de base du 6502. Les versions CMOS (65C02, 65816) ajoutent de nouvelles instructions mais restent retrocompatibles avec le code 6502 original. Ce document se concentre sur le 6502 original (NMOS), qui constitue le denominateur commun de toute la famille.

Contexte historique

Le 6502 est né d'une équipe d'ingénieurs de Motorola, menés par Chuck Peddle, ayant travaillé sur le Motorola 6800 (1974).

Insatisfaits du prix élevé du 6800 (environ 175 dollars) et désireux de créer un processeur abordable, ils quittèrent Motorola pour rejoindre MOS Technology en 1974. Le 6502 fut présenté au Wescon trade show en septembre 1975, ou il pouvait être acheté directement au comptoir pour 25 dollars, un prix qui stupéfie l'industrie.

Le 6502 a été adopte dans un nombre remarquable de systèmes emblématiques :

Ordinateurs personnels :

- Apple I (1976) : le premier ordinateur d'Apple, conçu par Steve Wozniak autour d'un 6502 a 1 MHz. Wozniak a choisi le 6502 en raison de son prix bas.

- Apple II (1977) : l'un des premiers ordinateurs personnels a connaître un succès commercial massif. 6502 a 1,023 MHz.

- L'Apple IIe (1983) et l'Apple IIc (1984) utilisent le 65C02.

- L'Apple IIGS (1986) utilise le 65C816 a 2,8 MHz.

- Commodore PET (1977) : premier ordinateur de Commodore, 6502 a 1 MHz

- Commodore VIC-20 (1980) : 6502A a 1,1 MHz, premier ordinateur vendu a plus d'un million d'exemplaires

- Commodore 64 (1982) : l'ordinateur personnel le plus vendu de tous les temps (environ 17 millions d'unités), utilisant un 6510 (variante du 6502) a 1,023 MHz (NTSC)

- Commodore 128 (1985) : 8502 a 1/2 MHz

- Atari 400 et 800 (1979) : 6502 a 1,79 MHz

- Atari XL/XE (1983-1985) : série de successeurs des 400/800, toujours bases sur le 6502

- BBC Micro (1981) : ordinateur éducatif très répandu au Royaume-Uni, 6502A a 2 MHz

- Acorn Electron (1983) : version économique du BBC Micro

- Oric-1 et Oric Atmos (1983) : 6502A a 1 MHz

- Ohio Scientific (1977) : gamme d'ordinateurs bases sur le 6502

Consoles de jeux :

- Atari 2600 (1977) : console de jeux légendaire, utilisant un 6507 (variante du 6502 avec bus d'adresses 13 bits) a 1,19 MHz

- Nintendo NES / Famicom (1983) : la console 8 bits la plus vendue au monde, utilisant un Ricoh 2A03 (clone du 6502 sans mode BCD) a 1,79 MHz (NTSC) / 1,66 MHz (PAL)

- Atari 7800 (1986) : variante du 6502C (Sally) a 1,79 MHz

- Atari Lynx (1989) : console portable, 65C02 a 4 MHz

- Super Nintendo / Super Famicom (1990) : Ricoh 5A22 (base sur le 65C816) a 3,58 MHz

Périphériques et systèmes embarqués :

- Lecteurs de disquettes Commodore (1541, 1571) : contiennent leur propre 6502 comme contrôleur

- Imprimantes Commodore

- Contrôleurs de disques Apple II (Disk II)

- Nombreux systèmes de contrôle industriel

- Bornes d'arcade (Atari, Namco,...)

- Instruments de musique électronique (Elektron SIDstation)

Le 6502 reste extrêmement populaire dans la communauté retro-informatique et parmi les amateurs d'électronique. Ben Eater a popularisé la construction d'ordinateurs 8 bits autour du 65C02 sur breadboard, et le WDC 65C02 et 65C816 sont toujours fabriques et vendus aujourd'hui (2026) par Western Design Center.

L'assembleur 6502 reste pertinent car :

- De très nombreux systèmes retro utilisent le 6502

- L'émulation de systèmes 6502 (C64, NES, Apple II, Atari) est extrêmement populaire

- Le 6502 est largement enseigne comme introduction a l'architecture des processeurs et a l'assembleur

- Le WDC 65C02/65C816 est toujours fabrique pour l'embarque

- Le projet DEV-COOLS cible le 6502 dans son compilateur multi-cible (TPCW32.PAS) et dispose d'un assembleur dédié (ASM6502.PAS), d'un compilateur C (CC6502.PAS) et d'un désassembleur (DIS6502.PAS).

Comparaison avec les autres processeurs de l'époque

Le 6502 était en concurrence directe avec l'Intel 8080/8085, le Zilog Z80 et le Motorola 6800 :

| Caractéristique | 6502 | 8080 | Z80 | 6800 |

|---|---|---|---|---|

| Année | 1975 | 1974 | 1976 | 1974 |

| Architecture | 8 bits | 8 bits | 8 bits | 8 bits |

| Bus données | 8 bits | 8 bits | 8 bits | 8 bits |

| Bus adresses | 16 bits | 16 bits | 16 bits | 16 bits |

| Espace adressable | 64 Ko | 64 Ko | 64 Ko | 64 Ko |

| Registres généraux | A, X, Y | A, B, C, | A, B, C, | A, B |

| D, E, H, L | D, E, H, L | |||

| + ensemble alternatif | ||||

| Modes d'adressage | 13 | 4 | 10 | 6 |

| Transistors | ~3 510 | ~4 500 | ~8 500 | ~4 100 |

| Fréquence typique | 1-2 MHz | 2 MHz | 2,5-4 MHz | 1-2 MHz |

| Prix initial | 25 $ | ~150 $ | ~25 $ (1978) | ~175 $ |

| Endianness | Little | Little | Little | Big |

| Pile | Page 1 | Mémoire | Mémoire | Mémoire |

| (256 octets) | (16 bits) | (16 bits) | (16 bits) |

Le 6502 se distingue par :

- Son prix extrêmement bas a sa sortie (25 $ vs 150-175 $)

- Son nombre réduit de transistors (conception très efficace)

- Ses modes d'adressage page zéro, qui compensent le faible nombre de registres en offrant un accès rapide a 256 octets

- Son pipeline simplifie a 2 étages, qui lui permet d'exécuter de nombreuses instructions en moins de cycles que ses concurrents malgré une fréquence d'horloge plus basse

- Sa pile limitée a 256 octets (page 1, adresses $0100-$01FF)

- L'absence de registres de 16 bits (pas d'arithmétique 16 bits native, contrairement au Z80 avec HL, BC, DE)

En termes de performances effectives, le 6502 a 1 MHz est souvent comparable au Z80 a 4 MHz pour de nombreuses tâches, grâce a son pipeline et a ses modes d'adressage efficaces.

Modèle de programmation

Le 6502 offre un modèle de programmation minimaliste mais efficace, compense par des modes d'adressage puissants :

Accumulateur (A) :

- Registre de 8 bits

- Seul registre pouvant effectuer des opérations arithmétiques (ADC, SBC) et logiques (AND, ORA, EOR)

- Destination et source principale pour les transferts de données (LDA, STA)

- Cible des opérations de décalage et rotation (ASL A, LSR A, ROL A, ROR A)

Registre d'index X :

- Registre de 8 bits

- Utilise comme index dans de nombreux modes d'adressage : page zéro indexe (ZPG,X), absolu indexe (ABS,X), indirect indexe ((IND,X))

- Peut être incrémenté (INX) et décrémenté (DEX)

- Peut être compare (CPX)

- Peut être transféré vers/depuis l'accumulateur (TAX, TXA) et vers/depuis le pointeur de pile (TSX, TXS)

Registre d'index Y :

- Registre de 8 bits

- Utilise comme index dans les modes d'adressage : page zéro indexe (ZPG,Y), absolu indexe (ABS,Y), indirect indexe ((IND),Y)

- Peut être incrémenté (INY) et décrémenté (DEY)

- Peut être compare (CPY)

- Peut être transféré vers/depuis l'accumulateur (TAY, TYA)

Pointeur de pile (SP, Stack Pointer) :

- Registre de 8 bits

- Pointe vers le prochain emplacement libre dans la pile

- La pile est située en page 1 (adresses $0100 a $01FF)

- L'adresse effective de pile est toujours $0100 + SP

- La pile croit vers le bas (SP décrémenté lors d'un PUSH)

- Initialement a $FD après un RESET (convention courante)

- Peut être initialise via TXS (transfert de X vers SP)

Compteur programme (PC, Program Counter) :

- Registre de 16 bits

- Pointe vers la prochaine instruction a exécuter

- Initialise a partir du vecteur RESET ($FFFC-$FFFD) au démarrage

- Automatiquement incrémenté lors de l'exécution des instructions

- Modifie par les instructions de saut (JMP), d'appel de sous-routine (JSR), de retour (RTS, RTI) et de branchement conditionnel (BCC, BCS, BEQ, BNE,...)

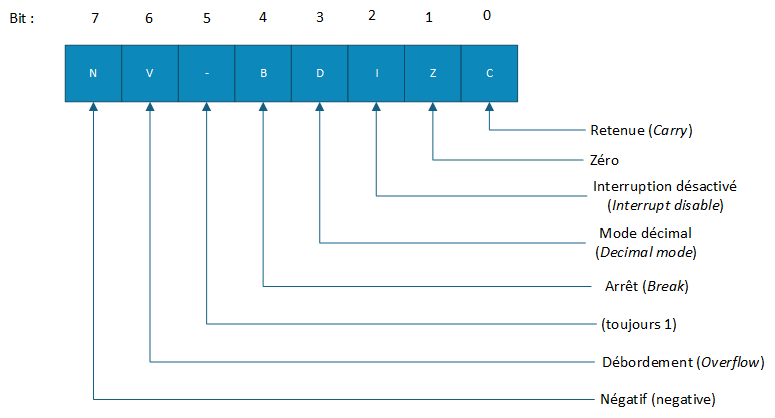

Registre d'état du processeur (P, Processor Status) :

- Registre de 8 bits contenant les drapeaux de condition et de contrôle :

- Représentation :

| Drapeaux | Description |

|---|---|

| Bit 7 : N (Negative) | Mis a 1 si le résultat est négatif (bit 7 du résultat = 1) |

| Bit 6 : V (Overflow) | Mis a 1 en cas de débordement de complément a deux |

| Bit 5 : (inutilisé) | Toujours a 1 |

| Bit 4 : B (Break) | Mis a 1 si l'interruption provient d'une instruction BRK |

| Bit 3 : D (Decimal) | Active le mode BCD (Binary Coded Decimal) pour ADC et SBC |

| Bit 2 : I (Interrupt) | Masque les interruptions IRQ quand mis a 1 |

| Bit 1 : Z (Zero) | Mis a 1 si le résultat est zéro |

| Bit 0 : C (Carry) | Retenue pour l'arithmétique, aussi utilisée par les décalages/rotations |

Le faible nombre de registres du 6502 est compense par l'utilisation de la page zéro ($0000-$00FF) comme un ensemble de 256 pseudo-registres accessibles en seulement 2 cycles d'horloge (au lieu de 4 pour un adressage absolu). Les programmeurs 6502 utilisent couramment la page zéro pour entreposer des pointeurs, des compteurs et des variables temporaires.

Ordre des octets (Endianness)

Le 6502 utilise l'ordre little-endian (poids faible en premier) :

- L'octet de poids faible est entreposé à l'adresse la plus basse

- Pour un mot de 16 bits $1234 a l'adresse $1000 :

| Adresse | Description |

|---|---|

| $1000 | $34 (octet de poids faible, Low Byte) |

| $1001 | $12 (octet de poids fort, High Byte) |

Cet ordre s'applique partout dans le 6502 :

- Les adresses 16 bits dans les instructions (format low-high)

- Les vecteurs d'interruption ($FFFA-$FFFF)

- L'adresse de retour empilée par JSR et les interruptions

- Les pointeurs en page zéro utilises par les modes d'adressage indirect

Exemples :

- L'instruction JMP $1234 est encodée : $4C $34 $12 (opcode, low byte, high byte)

- Le vecteur RESET aux adresses $FFFC-$FFFD :

- Un pointeur en page zéro aux adresses $80-$81 :

| Adresse | Description |

|---|---|

| $FFFC | $00 (low byte) → adresse de demarrage = $F000 |

| $FFFD | $F0 (high byte) |

| Adresse | Description |

|---|---|

| $0080 | $00 (low byte) → pointe vers $8000 |

| $0081 | $80 (high byte) |

C'est le même ordre que l'Intel 8080/8085, le Z80 et les x86. C'est l'ordre inverse du Motorola 6800 et du 68000 (big-endian), bien que le 6502 soit un descendant conceptuel du 6800.